# L64014 PC Card Bridge

# **Technical Manual**

Draft 7/28/98

Preliminary

This document is preliminary. As such, it contains data derived from functional simulations and performance estimates. LSI Logic has not verified either the functional descriptions, or the electrical and mechanical specifications using production parts.

This document contains proprietary information of LSI Logic Corporation. The information contained herein is not to be used by or disclosed to third parties without the express written permission of an officer of LSI Logic Corporation.

DB14-000042-00, First Edition (July 1998)

This document describes Revision A of LSI Logic Corporation's L64014 PC Card Bridge chip and will remain the official reference source for all revisions/releases of this product until rescinded by an update.

To receive product literature, call us at 1.800.574.4286 (U.S. and Canada); +32.11.300.531 (Europe); 408.433.7700 (outside U.S., Canada, and Europe) and ask for Department JDS; or visit us at http://www.lsilogic.com.

LSI Logic Corporation reserves the right to make changes to any products herein at any time without notice. LSI Logic does not assume any responsibility or liability arising out of the application or use of any product described herein, except as expressly agreed to in writing by LSI Logic; nor does the purchase or use of a product from LSI Logic convey a license under any patent rights, copyrights, trademark rights, or any other of the intellectual property rights of LSI Logic or third parties.

Copyright © 1997, 1998 by LSI Logic Corporation. All rights reserved.

# TRADEMARK ACKNOWLEDGMENT

LSI Logic logo design, MiniRISC, and CoreWare are registered trademarks of LSI Logic Corporation. All other brand and product names may be trademarks of their respective companies.

# Contents

| Preface                   |          |                              |                   |     |

|---------------------------|----------|------------------------------|-------------------|-----|

| Chapter 1<br>Introduction |          |                              |                   |     |

|                           | 1.1      | Overview                     |                   | 1-1 |

|                           | 1.2      | Features                     |                   | 1-3 |

| Chapter 2                 |          |                              |                   |     |

| <b>Functional Des</b>     | cription |                              |                   |     |

|                           | 2.1      | Overview                     |                   | 1-2 |

|                           | 2.2      | Host Interface               |                   | 1-3 |

|                           | 2.3      | DVD Decoder Interface and    | l Control         | 1-4 |

|                           |          | 2.3.1 GAMMA Correction       | on Look-up Table  | 1-5 |

|                           |          | 2.3.2 Content Scramble       | System (CSS)      | 1-6 |

|                           | 2.4      | Serial EEPROM Interface      |                   | 1-6 |

|                           | 2.5      | Zoomed Video (ZV) Port In    | terface           | 1-7 |

|                           | 2.6      | GPIO Interface               |                   | 1-8 |

|                           | 2.7      | Oscillator Control Interface |                   | 1-8 |

| Chapter 3<br>Registers    |          |                              |                   |     |

|                           | 3.1      | Overview                     |                   | 3-1 |

|                           | 3.2      | Direct I/O Registers         |                   | 3-2 |

|                           |          | 3.2.1 Control Index Reg      | jister (0x0)      | 3-2 |

|                           |          | 3.2.2 Control Data Regi      | ster (0x2)        | 3-3 |

|                           |          | 3.2.3 LSI Decoder Statu      | us Register (0x4) | 3-3 |

|     | 3.2.4    | LSI Low Index Address Register (0x8)             | 3-4  |

|-----|----------|--------------------------------------------------|------|

|     | 3.2.5    | LSI Data Register (0xA)                          | 3-4  |

|     | 3.2.6    | LSI High Index Address Register (0xC)            | 3-5  |

| 3.3 | Indexed  | I I/O Registers                                  | 3-6  |

|     | 3.3.1    | ID Register (0x00)                               | 3-7  |

|     | 3.3.2    | Mode Register (0x01)                             | 3-7  |

|     | 3.3.3    | IRQ Control Register (0x02)                      | 3-7  |

|     | 3.3.4    | IRQ Status Register (0x03)                       | 3-9  |

|     | 3.3.5    | LSI Control Register (0x06)                      | 3-9  |

|     | 3.3.6    | Oscillator and Audio Control Register (0x08)     | 3-10 |

|     | 3.3.7    | Video Control 0 Register (0x09)                  | 3-11 |

|     | 3.3.8    | Video Control 1 Register (0x0A)                  | 3-12 |

|     | 3.3.9    | Video Look-Up Table Data Port Register (0x0B)    | 3-14 |

|     | 3.3.10   | EEPROM Control Register (0x0C)                   | 3-14 |

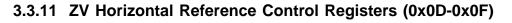

|     | 3.3.11   | ZV Horizontal Reference Control Registers        |      |

|     |          | (0x0D-0x0F)                                      | 3-16 |

|     | 3.3.12   | GPIO Control Register (0x10)                     | 3-17 |

|     | 3.3.13   | GPIO Pins Register (0x011)                       | 3-18 |

|     | 3.3.14   | CSS Command Register (0x12)                      | 3-19 |

|     | 3.3.15   | CSS Status Register (0x13)                       | 3-20 |

|     | 3.3.16   | CSS Key Register (0x14)                          | 3-21 |

| 3.4 | Configu  | ration Option Register                           | 3-21 |

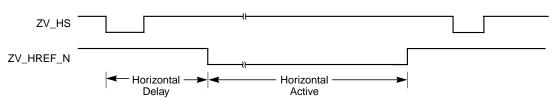

|     | 3.4.1    | Configuration Option Register (Attribute Memory, |      |

|     |          | Offset 0)                                        | 3-21 |

| 3.5 | Indirect | Access Registers                                 | 3-22 |

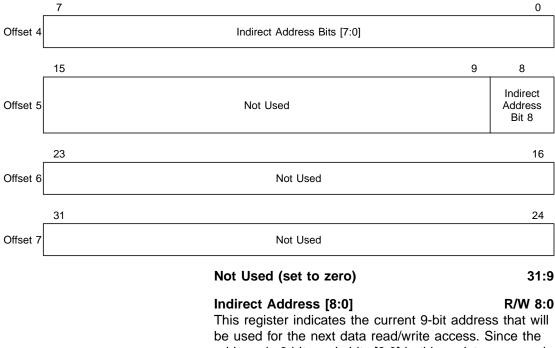

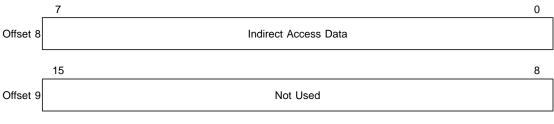

|     | 3.5.1    | Indirect Access Control Register (Common Memo    | -    |

|     |          | Offset 2-3)                                      | 3-22 |

|     | 3.5.2    | Indirect Access Address Register (Common Mem     | ory, |

|     |          | Offset 4-7)                                      | 3-23 |

|     | 3.5.3    | Indirect Access Data Register (Common Memory     |      |

|     |          | Offset 8-9)                                      | 3-24 |

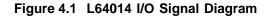

# Chapter 4 Signals

| 4.1 | Signals Groups          | 4-1 |

|-----|-------------------------|-----|

| 4.2 | Audio Interface         | 4-3 |

| 4.3 | Serial EEPROM Interface | 4-3 |

| 4.4 | Host Interface          | 4-4 |

|                             | 4.5 | GPIO Interface                                     | 4-5  |

|-----------------------------|-----|----------------------------------------------------|------|

|                             | 4.6 | L64020 DVD Decoder Interface                       | 4-5  |

|                             | 4.7 | Test Select                                        | 4-8  |

|                             | 4.8 | Oscillator and Clock Interface                     | 4-9  |

|                             | 4.9 | Zoomed Video Interface                             | 4-9  |

| Chapter 5<br>Specifications |     |                                                    |      |

|                             | 5.1 | Electrical Requirements                            | 5-2  |

|                             | 5.2 | AC Timing                                          | 5-3  |

|                             | 5.3 | Pin Summary                                        | 5-4  |

|                             | 5.4 | Packaging                                          | 5-7  |

| Figures                     |     |                                                    |      |

|                             | 1.1 | L64014 Typical Application                         | 1-2  |

|                             | 2.1 | L64014 Functional Block Diagram                    | 1-2  |

|                             | 2.2 | EEPROM Read Timing                                 | 1-7  |

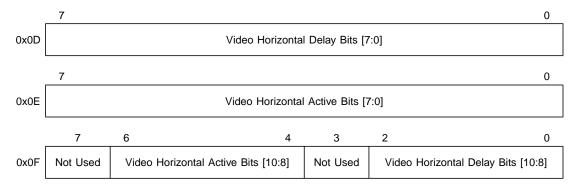

|                             | 3.1 | ZVHREF Output Timing                               | 3-16 |

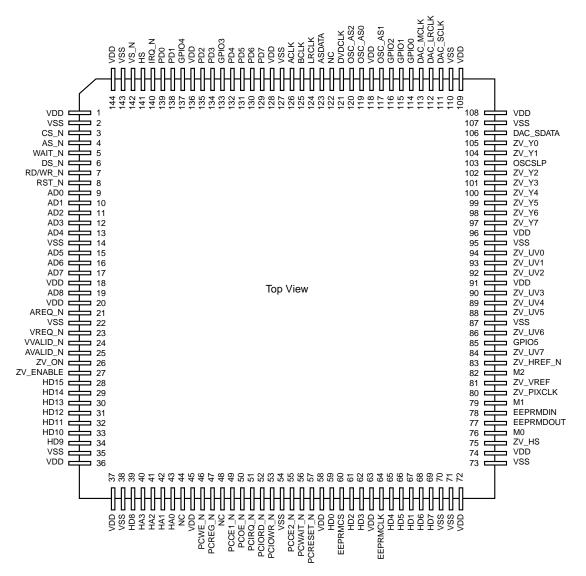

|                             | 4.1 | L64014 I/O Signal Diagram                          | 4-2  |

|                             | 5.1 | 144-pin TQFP Pinout                                | 5-4  |

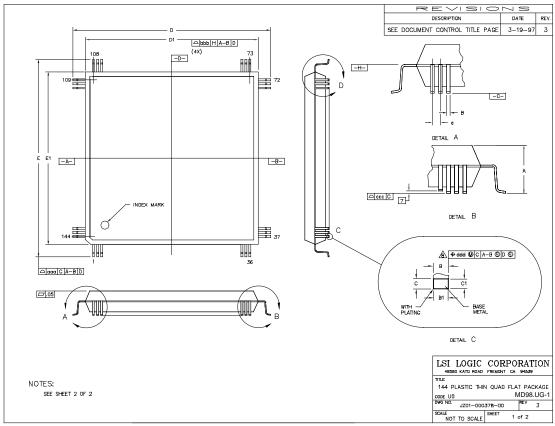

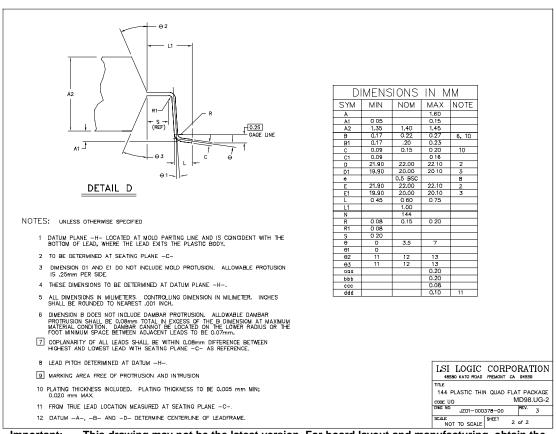

|                             | 5.2 | 144-pin TQFP (UG) Mechanical Drawing               | 5-7  |

| Tables                      |     |                                                    |      |

|                             | 2.1 | L64014 Read/Write Access Signals                   | 2-4  |

|                             | 2.2 | Horizontal and Vertical Sync Periods               | 2-5  |

|                             | 3.1 | Direct I/O Register Map                            | 3-2  |

|                             | 3.2 | Indexed I/O Register Map                           | 3-6  |

|                             | 5.1 | Absolute Maximum Ratings                           | 5-2  |

|                             | 5.2 | Recommended Operating Conditions                   | 5-2  |

|                             | 5.3 | Capacitance                                        | 5-3  |

|                             | 5.4 | DC Characteristics                                 | 5-3  |

|                             | 5.5 | Alphabetical Pin List for the 144-pin TQFP Package | 5-5  |

# Preface

This book is the primary reference and technical manual for the L64014 PC Card Bridge. It contains a complete functional description of the L64014 as well as complete physical and electrical specifications.

# Audience

This document assumes that you have some familiarity with the specifications of DVD and related digital A/V devices. The people who benefit from this book are:

- Engineers and managers who are evaluating the L64014 chip for possible use in a system

- Engineers who are designing the L64014 chip into a system

# Organization

This document has the following chapters and appendixes:

- Chapter 1, Introduction, presents an overview of the L64014.

- Chapter 2, Functional Description, describes the functional blocks within the L64014.

- Chapter 3, Registers, describes the direct and indexed I/O registers, as well as the PC Card configuration and indirect access registers.

- Chapter 4, Signals, defines each of the L64014's I/O signals.

- Chapter 5, Specifications, presents the L64014's electrical characteristics, requirements, and timing, as well as its pinout and package specifications.

# **Related Publications**

PC Card Standard

*L64020 DVD Audio/Video Decoder Technical Manual*, May 1998, Document No. DB14-000028-00

# **Conventions Used in This Manual**

The first time a word or phrase is defined in this manual, it is *italicized*.

The word *assert* means to drive a signal true or active. The word *deassert* means to drive a signal false or inactive.

Hexadecimal numbers are indicated by the prefix "0x" before the number—for example, 0x32CF. Binary numbers are indicated by the prefix "0b" before the number—for example, 0b0011.0010.1100.1111.

# Chapter 1 Introduction

This chapter introduces the L64014 PC Card Bridge and includes these sections:

- Section 1.1, "Overview," page 1-1

- Section 1.2, "Features," page 1-3

# 1.1 Overview

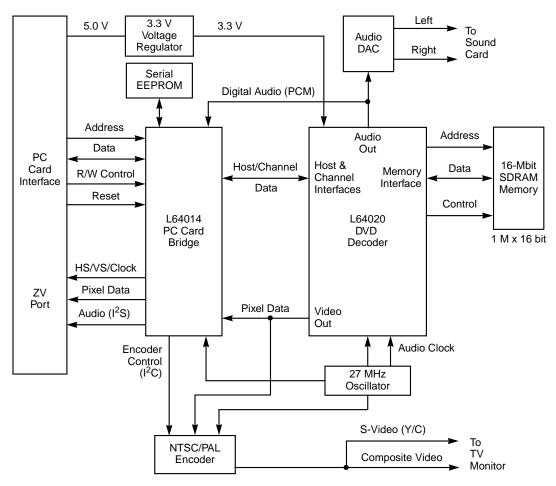

The L64014 PC Card Bridge chip provides a PC Card solution for interfacing a DVD decoder, such as LSI Logic's L64020, with a low-power notebook computer that is equipped with a Zoomed Video (ZV) port. Figure 1.1 shows a block diagram of the L64014 in a typical system application, which incorporates LSI Logic's L64020 DVD A/V Decoder. The decoded video output can be viewed on the PC notebook's monitor, or on an external TV screen by means of an NTSC/PAL video encoder. The L64014 supplies decompressed audio through the ZV port as I<sup>2</sup>S formatted stereo. The L64014's host interface provides host access to its internal control registers, as well as those of the DVD decoder and the NTSC/PAL encoder (I<sup>2</sup>C). Its DVD decoder interface includes a look-up table for gamma correction on the YUV pixel data for ZV output. The DVD decoder interface also includes a content scramble system (CSS) module for disc and title key decoding.

Figure 1.1 L64014 Typical Application

# 1.2 Features

- PC Card interface

- ♦ L64020 DVD A/V Decoder interface

- Software-configurable ZV port interface

- Serial EEPROM interface

- Frequency-selectable audio clock control

- ZV signal gamma correction using software look-up table

- External ZV port control

- CSS decoding for DVD playback

- NTSC/PAL encoder interface (I<sup>2</sup>C bus control)

- NTSC/PAL video sync from a single 27-MHz clock

- Accepts AES digital audio format and issues I<sup>2</sup>S data (ZV port)

- Six GPIO pins

- 144-pin TQFP package

# Chapter 2 Functional Description

This chapter provides a functional description of the L64014 and includes these sections:

- Section 2.1, "Overview," page 2-2

- Section 2.2, "Host Interface," page 2-3

- Section 2.3, "DVD Decoder Interface and Control," page 2-4

- Section 2.4, "Serial EEPROM Interface," page 2-6

- Section 2.5, "Zoomed Video (ZV) Port Interface," page 2-7

- Section 2.6, "GPIO Interface," page 2-8

- Section 2.7, "Oscillator Control Interface," page 2-8

# 2.1 Overview

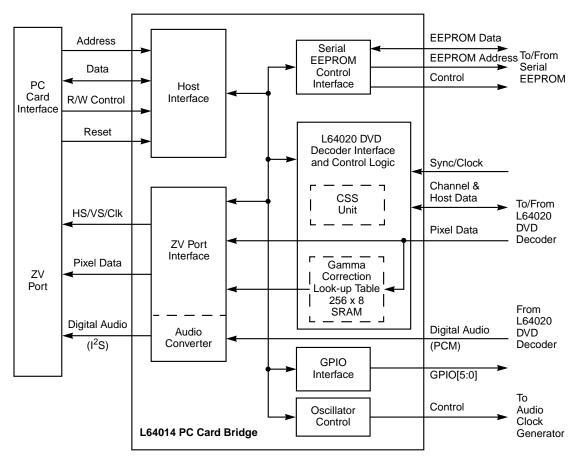

Figure 2.1 shows a functional block diagram of the L64014. The sections that follow this figure describe the functionality of each block.

# 2.2 Host Interface

This interface provides the host with access to the L64014 registers for controlling system-level capabilities such as interrupts, reset, wait, and port enabling. Through this interface, the host can read from and write to the direct and indexed registers in the L64014. The host can also access registers in the DVD decoder chip, as well as read data from the serial EEPROM (see Section 2.4, "Serial EEPROM Interface.")

The L64014 Host Interface supports host access to three PC Card memory address spaces:

- Attribute Memory Space

- Common Memory Space

- I/O Address Space

The host can access the 16-bit PC Card Attribute Memory Space with memory read and write operations that occur while the PCREG\_N signal is LOW. This address space is defined only for bytes located at even byte addresses. It is the primary location for the Card Information Structure (CIS) and for the PC Card configuration registers, in particular, the Configuration Option Register (Offset 0, see Section 3.4, "Configuration Option Register.")

The Common Memory Space is accessed by the host with memory read and write operations that occur while the PCREG\_N signal is HIGH. This address space is defined for bytes located at both even and odd byte addresses. The Indirect Access Registers (Offset 2-9) are located in this memory space (Section 3.5, "Indirect Access Registers.")

The host accesses the I/O Address Space by asserting either the I/O Read signal (PCIORD\_N), or the I/O Write signal (PCIOWR\_N), while the PCREG\_N signal and at least one card enable signal (PCCE1\_N and/or PCCE2\_N) are LOW. The I/O Address Space contains the six L64014 direct I/O registers, which are used to control the bridge chip. It also includes the 18 indexed I/O registers (for details, see Section 3.3, "Indexed I/O Registers.")

The L64014 uses the PC Card Indirect Access Registers to support read operations from the EEPROM. These registers are required since the

L64014 only uses four address lines to access the EEPROM's 512 x 8 bits of memory.

Through the Host Interface, the L64014 responds to the following 8-bit commands:

- I/O read and write commands

- Attribute memory read and write commands

- Common memory read and write commands

Table 2.1 shows the active signals that are used for read/write access to/from the L64014.

| Table 2.1 L64014 Rea | d/Write Access Signals |

|----------------------|------------------------|

|----------------------|------------------------|

| Function               | PCREG_N<br>(DACK) | PCCEx_N | PCOE_N | PCWE_N | PCIORD_N | PCIOWR_N |

|------------------------|-------------------|---------|--------|--------|----------|----------|

| I/O Read               | L                 | L       | Н      | Н      | L        | Н        |

| I/O Write              | L                 | L       | н      | н      | н        | L        |

| Attribute Memory Read  | L                 | L       | L      | н      | н        | Н        |

| Attribute Memory Write | L                 | L       | н      | L      | н        | Н        |

| Common Memory Read     | н                 | L       | L      | Н      | н        | Н        |

| Common Memory Write    | Н                 | L       | н      | L      | н        | н        |

# 2.3 DVD Decoder Interface and Control

The DVD Decoder Interface and Control logic provides access to the DVD Decoder's indexed registers and data ports. The interface and control functions handle register addressing, port enabling, reset, wait, and interrupt control. The control logic generates the required horizontal and vertical synchronization signals (HS and VS\_N) for the DVD Decoder. The interrupt control logic receives interrupt requests from the DVD Decoder and relays them to the host.

The HS and VS\_N signals are active HIGH outputs that are derived from the DVDCLK input signal. The HS pulse width is 63 clock cycles,

whereas the VS\_N pulse width is ??? clock cycles. The video mode (NTSC/PAL/PAL24) determines the horizontal and vertical sync periods as shown in Table 2.2. These video modes can be selected by writing to bits [1:0] in the Video Control 1 Register (0x0A).

| Video<br>Mode | Horizontal Sync Period<br>(Clock Cycles) | Vertical Sync Period<br>(Clock Cycles) |

|---------------|------------------------------------------|----------------------------------------|

| NTSC          | 1716                                     | 525                                    |

| PAL           | 1728                                     | 625                                    |

| PAL24         | 1925                                     | 585                                    |

# Table 2.2 Horizontal and Vertical Sync Periods

There are two byte-wide data paths between the DVD Decoder and the L64014. Both paths share the same L64014 data port: AD[7:0].

One data path is for Host access of the registers inside the DVD decoder; control for this path is provided by the AS\_N, DS\_N, and RD/WR\_N signals. The host indirectly accesses DVD decoder registers through the L64014 by writing their addresses to the L64014's LSI Low and High Index Address registers (0x8 and 0xC). When data is read from or written to the LSI Data Register (0xA), the L64014 generates a host/DVD decoder read/write cycle.

The other data path serves as the DVD decoder input path for the encoded MPEG bitstream, which is also called the Channel Data path. This path uses the VVALID\_N and AVALID\_N signals to indicate that valid data is present on the AD[7:0] bus. Channel data is written to the LSI Decoder Channel Data Register (0x4, W). The audio and video channels are selected by writing to bit 6 in the LSI Control Register (0x06).

# 2.3.1 GAMMA Correction Look-up Table

The L64014 DVD Decoder Interface includes a 256 x 8-bit SRAM that contains gamma correction information. The information is arranged in a look-up table. When the gamma correction look-up function is enabled, the incoming 8-bit pixel data from the DVD Decoder is used as the

address for accessing the correct SRAM location. Each SRAM location contains gamma corrected video luminance information. The L64014 accesses the information in the look-up table, and sends this information to the ZV port (through ZV\_YV[7:0]) in place of the luminance video data that originated from the L64020.

The Video Look-up Table Data Port Register (0x0B, W) provides a path for writing gamma correction data into SRAM. This data port is always enabled. By setting bit 2 in the Video Control 1 Register (0x0A), the host can enable read operations from the gamma correction look-up table.

# 2.3.2 Content Scramble System (CSS)

The L64014 DVD Decoder Interface features a CSS component for descrambling DVD disc and title keys. These keys provide access to protected data on the DVD disc. The CSS Key Register (0x14) holds the 8-bit disc and title keys during the descrambling process. The host can control CSS functions by writing to the CSS Command Register (0x12). It can also monitor CSS operations by reading the CSS Status Register (0x13).

# 2.4 Serial EEPROM Interface

The L64014 EEPROM Interface provides a serial interface to the external EEPROM. Because this is a serial interface, the memory pinout requirements are greatly reduces.

The EEPROM contains card information structure (CIS) data. The host can read or write CIS data through the L64014 in serial, as well as in parallel, one byte at a time. Typically, CIS transfers are parallel operations. Setting the bits in the EEPROM Control Register (0x0C) enables the host to write data to the EEPROM. Software is required for the host to directly control the EEPROM signals.

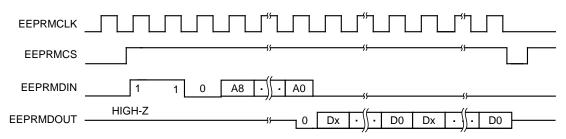

Figure 2.2 shows the timing for read operations. The host uses the Indirect Access Address Register to address the EEPROM (see Section 3.5, "Indirect Access Registers".) Since the L64014 Serial EEPROM Interface always sends 9 address bits, the dimensions of the EEPROM memory space must be 512 x 8 bits. Only the least significant 9 bits of the Indirect Access Address Register (Common Memory offset 4-7) are used for addressing the EEPROM.

The host initiates parallel read transfers by executing the PC Card Read Attribute Memory command, or the Read Common Memory command. When one of these read commands is issued, the L64014 reads the data serially from the EEPROM, assembles it, and then sends it to the host one byte at a time. While accessing attribute memory, the host only reads the even bytes of the EEPROM address space. While accessing common memory, the host reads both the even and odd bytes of the EEPROM address space.

Note: The EEPROM must have a minimum clock speed of 3 MHz.

# 2.5 Zoomed Video (ZV) Port Interface

The ZV port interface supplies the host system with decoded 8-bit or 16bit YUV pixel data and I<sup>2</sup>S formatted digital serial audio data. The L64014 zoomed video logic also outputs a horizontal sync (ZV\_HREF\_N) signal, a vertical sync (ZV\_VREF) signal, and a pixel clock (ZV\_PIXCLK) signal. These signals are derived from the 27-MHz system clock that is used by the L64020 DVD A/V Decoder.

The host can select the pixel data output width by writing to bit 4 in the Video Control 0 Register (0x09). The L64014 sends 8-bit pixel data when bit 4 is zero; setting this bit configures the L64014 to send 16-bit pixel data. In 8-bit mode, YUV data is sent on the  $ZV_Y[7:0]$  lines. In 16-bit mode, luminance (Y) data is sent on the  $ZV_Y[7:0]$  lines and chrominance (UV) data is sent on the  $ZV_U[7:0]$  lines.

For 8-bit video output, ZV\_PIXCLK runs at 27 MHz. For 16-bit video output, the 27-MHz clock can be divided to generate a 13.5-MHz ZV\_PIXCLK signal by setting bit 2 in the Video Control 0 Register (0x09).

The host can also enable optional gamma correction on pixel data for ZV output by setting bit 2 in the Video Control 1 Register (0x0A).

The L64020 DVD Decoder supplies 32-bit sign-extended PCM audio data in right-justified frames. By setting bit 4 in the Oscillator and Audio Control Register (0x08), the L64014's ZV interface logic converts the PCM data to digital stereo  $I^2S$ . The SDATA signal carries the  $I^2S$  serial audio data to the ZV port. A DAC within the PC converts the  $I^2S$  data to analog for playback on speakers.

# 2.6 GPIO Interface

The L64014 GPIO Interface comprises six general purpose I/O lines (GPIO[5:0]). These lines can be used to supply  $I^2C$  control to an external NTSC/PAL video encoder. By setting bits in the GPIO Control (0x10) and GPIO Pins (0x11) indexed registers, the host can send data across the GPIO[5:0] lines.

# 2.7 Oscillator Control Interface

The L64014 Oscillator Control Interface logic provides host control of an external oscillator. The L64014 receives a 27-MHz system clock from this oscillator. By writing to the Oscillator and Audio Control Register (0x08), bits [3:0], the host can select the audio clock frequency, as well as place the oscillator in Sleep mode.

# Chapter 3 Registers

This chapter describes the L64014 internal registers and includes the following sections:

- Section 3.1, "Overview," page 3-1

- Section 3.2, "Direct I/O Registers," page 3-2

- Section 3.3, "Indexed I/O Registers," page 3-6

- Section 3.4, "Configuration Option Register," page 3-21

- Section 3.5, "Indirect Access Registers," page 3-22

# 3.1 Overview

The L64014 registers are located in three distinct address spaces:

- Attribute Memory Space

- Common Memory Space

- ♦ I/O Address Space

The Attribute Memory Space contains the Configuration Option Register (offset 0). The Indirect Access Registers (offset 2-9) are located in the Common Memory Space. The I/O Address Space contains the L64014-specific direct and indexed I/O registers. The host can address these registers using read/write commands. Indirect addressing reduces pin requirements; the L64014 only uses four address lines to access these memory spaces.

Note: The L64014 must be configured by the system before the I/O Address Space can be accessed.

The L64014 features six direct and 18 indexed I/O registers. The HA[3:0] pins supply host access to the direct I/O registers. Two of the direct I/O

registers provide read/write access to the L64014's indexed I/O registers. The other direct I/O registers provide read/write access to the registers in the L64020 DVD A/V Decoder. They also supply status information on the DVD decoder interface.

# 3.2 Direct I/O Registers

Table 3.1 lists the six direct I/O registers and their addresses. Each register is addressed using a 4-bit address. (Note that the L64014 does not use PC Card address bits 4 and 5 (HA4, HA5).)

| Offset<br>Address | R/W | Bit<br>Width | Register Name                   |  |

|-------------------|-----|--------------|---------------------------------|--|

| 0x0               | R/W | 5            | Control Index Register          |  |

| 0x2               | R/W | 8            | Control Data Register           |  |

| 0x4               | R   | 4            | LSI Decoder Status Register     |  |

|                   | W   | 8            | Channel Data Register           |  |

| 0x8               | R/W | 8            | LSI Low Index Address Register  |  |

| 0xA               | R/W | 8            | LSI Data Register               |  |

| 0xC               | R/W | 1            | LSI High Index Address Register |  |

Table 3.1 Direct I/O Register Map

# 3.2.1 Control Index Register (0x0)

| 7        | 5 | 4                            | 0 |

|----------|---|------------------------------|---|

| Not Used |   | Indexed I/O Register Address |   |

# Not Used

# Indexed I/O Register Address

This register contains the address for a specified indexed I/O register. (See Table 3.2 for a list the Indexed I/O Register addresses.) The Control Data Register (0x2) writes and reads data to and from the I/O register whose address is referenced in this register.

7:5

R/W 4:0

Not Used

The read portion of this register contains DVD decoder status information. The write portion contains channel data.

This register reads data from and writes data to the indexed I/O register whose address is specified in the

| RE  | Ready Error R 3<br>The L64014 sets this bit when the Wait state times out<br>(WAIT_N is LOW for 128 DVDCLK cycles). The Ready<br>Error bit is cleared by setting bit 5 in the LSI Control Reg-<br>ister (0x06). |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | Wait R 2<br>This bit is cleared when the WAIT_N input signal (pin 5)<br>from the DVD decoder is asserted (LOW).                                                                                                 |

| ARQ | Audio Request R 1<br>This audio request bit is cleared when the AREQ_N input<br>signal (pin 21) from the DVD decoder is asserted (LOW).                                                                         |

| VRQ | Video RequestR 0This video request bit is cleared when the VREQ_N inputsignal (pin 23) from the DVD decoder is asserted (LOW).                                                                                  |

|     | Channel Data W 7:0<br>When 8-bit channel data is written to this register, the<br>L64014 outputs the data to the DVD decoder through the                                                                        |

| i Decoder Status Register (0x4) |    |      |     |  |  |  |  |

|---------------------------------|----|------|-----|--|--|--|--|

| 4                               | 3  | 2    | 1   |  |  |  |  |

| Not Used                        | RE | Wait | ARQ |  |  |  |  |

Channel Data

Control Index Register (0x0).

Control Data

**Control Data**

## Status Register (AvA) 3.2.3 LSI De 40

# 3.2.2 Control Data Register (0x2)

7

Read

Write

7

| L64014 PCMCIA      | BridgeTechnical Manual                                                |

|--------------------|-----------------------------------------------------------------------|

| July 1998 - Rev. A | Copyright © 1997, 1998 by LSI Logic Corporation. All rights reserved. |

R/W 7:0

0

VRQ

R 7:4

0

AD[7:0] bus. The channel control signals (AREQ\_N, VREQ\_N, AVALID\_N, and VVALID\_N) strobe the bitstream data into the L64020. Setting or clearing bit 6 in the LSI Control Register (0x06) selects the video channel or the audio channel, respectively.

# 3.2.4 LSI Low Index Address Register (0x8)

| 1 | 0                                                                                                                                                                                                                                                                                   |

|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | Low Index Address                                                                                                                                                                                                                                                                   |

|   | Low Index Address R/W 7:0<br>This dual-purpose register holds either of the two follow-<br>ing types of address information:                                                                                                                                                        |

|   | <ul> <li>the lower eight bits of the of the 9-bit LSI indexed I/O<br/>register address</li> </ul>                                                                                                                                                                                   |

|   | <ul> <li>the address of a SRAM location that contains gamma<br/>correction data for YUV output through the ZV port</li> </ul>                                                                                                                                                       |

|   | In the first case, when host data is written to or read from<br>the LSI Data Register (0xA), it is cycled to/from the<br>decoder using the address that is specified by concate-<br>nating the contents of this register with that of the LSI<br>High Index Address Register (0xC). |

|   | In the second case, the L64014 stores the gamma correction information in a RAM look-up table. When data is written to the Video Look-up Table Data Port Register (0x0B), it is cycled to the look-up table SRAM using the address specified by this register.                      |

# 3.2.5 LSI Data Register (0xA)

| 7 |                  | 0 |

|---|------------------|---|

|   | DVD Decoder Data |   |

|   |                  |   |

# **DVD Decoder Data**

# R/W 7:0

The host uses this register to read/write data from/to the DVD decoder register whose address is obtained by concatenating the contents of the LSI Low and High Index Address Registers (0x8 and 0xC, respectively). When this register is written or read, its contents is sent across the AD[7:0] lines. These host/decoder data transfers are controlled using the AS\_N, CS\_N, DS\_N, and RD/WR\_N signals.

# 3.2.6 LSI High Index Address Register (0xC)

| 7 |          | 1 | 0                     |

|---|----------|---|-----------------------|

|   | Not Used |   | High Index<br>Address |

# **High Index Address**

# R/W 0

This register holds the highest bit of the 9-bit LSI indexed register address. When host data is written to or read from the LSI Data Register (0xA), it is cycled to/from the decoder using the address that is specified by concatenating the contents of this register with that of the LSI Low Index Address Register (0x8).

# 3.3 Indexed I/O Registers

The L64014 includes 18 indexed I/O registers. Table 3.2 provides a map of the indexed registers.

| Table 3.2 | Indexed | I/O | Register | Мар |

|-----------|---------|-----|----------|-----|

|-----------|---------|-----|----------|-----|

| Offset<br>Address | R/W | Bit<br>Width | Register Name                          |

|-------------------|-----|--------------|----------------------------------------|

| 0x00              | R   | 8            | ID Register                            |

| 0x01              | R   | 8            | Mode Register                          |

| 0x02              | R/W | 8            | IRQ Control Register                   |

| 0x03              | R   | 8            | IRQ Status Register                    |

| 0x06              | R/W | 8            | LSI Control Register                   |

| 0x08              | R/W | 6            | Oscillator and Audio Control Register  |

| 0x09              | R/W | 5            | Video Control 0 Register               |

| 0x0A              | R/W | 8            | Video Control 1 Register               |

| 0x0B              | W   | 8            | Video Look-up Table Data Port Register |

| 0x0C              | R/W | 4            | EEPROM Control Register                |

| 0x0D              | R/W | 8            | Video Horizontal Delay Register        |

| 0x0E              | R/W | 8            | Video Horizontal Active Register       |

| 0x0F              | R/W | 7            | Video Horizontal High Bits Register    |

| 0x10              | R/W | 6            | GPIO Control Register                  |

| 0x11              | R/W | 6            | GPIO Pins Register                     |

| 0x12              | R/W | 5            | CSS Command Register                   |

| 0x13              | R/W | 2            | CSS Status Register                    |

| 0x14              | R/W | 8            | CSS Key Register                       |

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

| 1 | 1 | 0 | 1 | 1 | 1 | 0 | 1 |

ID Register R 7:0 This read-only register is hardcoded with the L64014 device ID, which is 0xDD.

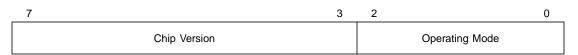

# 3.3.2 Mode Register (0x01)

# **Chip Version**

# R 7:3

This read-only field contains the chip version number.

# Operating Mode

# R 2:0

This read-only field specifies the L64014 operating mode. These bits are set to 0b010 for normal PC Card operation.

| Bits 2:0 | Function                         |

|----------|----------------------------------|

| 010      | Normal PC Card operation         |

| 011      | Reserved for 3-state output test |

| 111      | Reserved for scan flip-flop test |

# 3.3.3 IRQ Control Register (0x02)

| 7    | 6        | 5   | 4   | 3  | 2  | 1        | 0 |

|------|----------|-----|-----|----|----|----------|---|

| IVVE | Reserved | IDE | ILT | IM | IE | Reserved |   |

The contents of this register controls interrupt requests (IRQs). The PCIRQ\_N output signal is generated from the VS\_N and IRQ\_N input signals, which are passed directly through the DVD decoder interface.

| IVVE | IRQ Video Vertical Sync Enable<br>Setting this bit allows the VS_N signal to generat<br>PC_IRQ_N interrupt output. Clearing this bit disable<br>feature and clears bit 6 in the IRQ Status Register                                     | les this           |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

|      | Reserved (must be set to 0)                                                                                                                                                                                                             | 6                  |

| IDE  | <b>IRQ DVD Enable</b><br>Setting this bit allows the IRQ_N signal to genera<br>PC_IRQ_N interrupt output. Clearing this bit disable<br>feature and clears bit 4 in the IRQ Status Register                                              | les this           |

| ILT  | <b>IRQ Low True</b><br>Setting this bit changes the interrupt polarity of th<br>PCIRQ_N output signal to active HIGH. Clearing<br>maintains the interrupt polarity of the PCIRQ_N of<br>signal as active LOW (normal PC Card operation) | this bit<br>output |

| М    | <b>IRQ Mask</b><br>Setting this bit masks the interrupts. Clearing this<br>enables the interrupts. Bit 2 of this register must<br>for this bit to mask the interrupts.                                                                  |                    |

| IE   | <b>IRQ Enable</b><br>Setting this bit enables the interrupts. Clearing th disables the interrupts.                                                                                                                                      | R/W 2<br>is bit    |

|      | Reserved (must be set to 0)                                                                                                                                                                                                             | 1:0                |

# 3.3.4 IRQ Status Register (0x03)

| 7        | 6            | 5        | 4      | 3 | 2   | 1    | 0 |

|----------|--------------|----------|--------|---|-----|------|---|

| Not Used | VID<br>VSIRQ | Reserved | DVDIRQ |   | Not | Jsed |   |

This register contains the interrupt status information. It is a latched version of each IRQ.

|          | Not Used                                                                                                                                                                                                           | 7          |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| VIDVSIRQ | Video Interrupt<br>When set, this bit indicates that an interrupt is init<br>the falling edge of the DVD decoder VS_N signal<br>is cleared when bit 7 in the IRQ Control Registe<br>is cleared.                    | . This bit |

|          | Reserved                                                                                                                                                                                                           | 5          |

| DVDIRQ   | <b>DVD Decoder Interrupt</b><br>When set, this bit indicates that an interrupt is init<br>the falling edge of the DVD decoder IRQ_N sigr<br>bit is cleared when bit 5 in the IRQ Control Reg<br>(0x02) is cleared. | nal. This  |

|          | Not Used                                                                                                                                                                                                           | 3:0        |

# 3.3.5 LSI Control Register (0x06)

|     | 7    | 6    | 5  | 4 |          | 1 | 0  |

|-----|------|------|----|---|----------|---|----|

| Not | Used | DSVC | RR |   | Not Used |   | DR |

This register controls DVD decoder channel selection, decoder reset, and ready error reset.

|      | Not Used                                      | 7            |

|------|-----------------------------------------------|--------------|

| DSVC | Decoder Select Video Channel                  | R/W 6        |

|      | This bit selects which A/V channel data contr | ol signals   |

|      | (AVALID_N or VVALID_N) are used when wr       | iting to the |

|      | Channel Data Register (0x4, W).               |              |

Setting this bit selects the video channel (VVALID\_N is used). Clearing this bit selects the audio channel (AVALID\_N is used).

| RR | Ready ResetR/W 5Setting this bit resets Ready Error (bit 3) in the LSIDecoder Status Register (0x4, R). |

|----|---------------------------------------------------------------------------------------------------------|

|    | Not Used 4:1                                                                                            |

| DR | LSI Decoder Reset R/W 0<br>This bit controls the DVD decoder reset signal, RST_N<br>(pin 8).            |

|    | Clearing this bit drives RST_N LOW, which resets the DVD decoder. Setting this bit drives RST_N HIGH.   |

# 3.3.6 Oscillator and Audio Control Register (0x08)

| <br>7 | 6    | 5   | 4   | 3     | 2    | 1    | 0    |

|-------|------|-----|-----|-------|------|------|------|

| Not L | lsed | AF1 | AF0 | SLEEP | AFS2 | AFS1 | AFS0 |

This register provides oscillator frequency and audio control functions.

|       | Not Used                                                                                                                                                                                                                                               | 7:6                  |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| AF1   | Audio Form 1<br>Reserved                                                                                                                                                                                                                               | R/W 5                |

| AF0   | Audio Form 0<br>Setting this bit controls the L64014 to convert D<br>decoder digital PCM audio data (ASDATA) to $I^2$<br>before sending it to the SDATA output. Clearing<br>causes the DVD decoder to send the ASDATA<br>directly to the SDATA output. | S format<br>this bit |

| SLEEP | <b>Oscillator Sleep Mode Control</b><br>This bit directly drives the Oscillator Sleep outp<br>(OSC_SLP, pin 103). It can be used to disable<br>nal DVDCLK and audio clocks to reduce power of<br>tion.                                                 | the exter-           |

|       | Setting this bit asserts OSC_SLP (HIGH), there enabling Oscillator Sleep mode. Clearing this b                                                                                                                                                         | •                    |

OSC\_SLP LOW, thereby returning the oscillator to normal operation.

AFS2:0 Audio Frequency Select 2:0 R/W 2:0 The frequency select bits, AFS2:0, directly control pins 120 (OSC\_AS2), 117 (OSC\_AS1), and 119 (OSC\_AS0), respectively. These pins connect to the external audio clock generator.

When using a Microclock 2744 or 2745-21 oscillator, these three bits select the audio master clock frequency as shown below:

# AFS2 AFS1 AFS0 Audio Clock Frequency (in MHz)

| 0 | 0 | 0 | 12.288  |  |

|---|---|---|---------|--|

| 0 | 0 | 1 | 11.2896 |  |

| 0 | 1 | 0 | 8.192   |  |

| 0 | 1 | 1 | 24.576  |  |

| 1 | 0 | 0 | 8.192   |  |

| 1 | 0 | 1 | 16.9344 |  |

| 1 | 1 | 0 | 18.432  |  |

| 1 | 1 | 1 | 11.2896 |  |

# 3.3.7 Video Control 0 Register (0x09)

| 7 |          | 5     | 4                         | 3                              | 2                                                     | 1           | 0         |

|---|----------|-------|---------------------------|--------------------------------|-------------------------------------------------------|-------------|-----------|

|   | Not Used |       | ZV16Bit                   | ZVCLK<br>INV                   | ZVCLK13                                               | SWAP        | VSBT      |

|   |          |       | Not Used                  |                                |                                                       |             | 7:5       |

|   | ZV16     | Bit   | In this moo<br>(pins 105, | le, Y pixel d                  | ne ZV port e<br>lata is made<br>7) and UV pi<br>, 84) | available o | n ZV_Y7:0 |

|   |          |       | mode. In th               |                                | ed, the ZV p<br>UV pixel dat<br>04, 102:97)           |             |           |

|   | ZVC      | LKINV | •                         | s bit inverts<br>bit is cleare | the ZV_PIX<br>d, the ZV_P                             | •           | •         |

| ZVCLK13 | <b>ZV Clock 13 Select</b><br>When this bit is set, a 13.5-MHz clock is output on<br>ZV_PIXCLK (pin 80) for 16-bit mode operation. Whe<br>bit is cleared, a 27-MHz clock is output on ZV_PIX<br>(pin 80) for 8-bit mode operation. | n this |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| FLDSWAP | <b>Field Swap</b><br>Setting this bit starts the odd field on line 1 (bottom<br>play field becomes odd field). Clearing this bit start<br>odd field on line zero (top display field becomes od<br>field).                         | s the  |

| VSBT    | <b>VS Type B</b><br>When this bit is set, bottom/top field toggling for ear<br>field is made available on VS_N (pin 142). Clearing<br>bit allows video sync to be generated from the 27-                                          | g this |

clock for output on VS\_N (pin 142).

# 3.3.8 Video Control 1 Register (0x0A)

| _ | 7   | 6   | 5    | 4                                                                                                                                                                                                                                                                                 | 3     | 2                           | 1 | 0  |  |

|---|-----|-----|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----------------------------|---|----|--|

|   | ZVE | ZVO | ZHSN | ZHRN                                                                                                                                                                                                                                                                              | ZVRFN | ELUT                        | V | MS |  |

|   |     | ZV  | E    | ZV EnableR/W 7Setting this bit enables zoomed video output on the hostZV port. Clearing this bit isolates all ZV signal pins                                                                                                                                                      |       |                             |   |    |  |

|   | ZVO |     |      | <b>ZV Override R/M</b><br>This bit, in combination with bit 7 of this register, control<br>access to the ZV port. The ZV_ENABLE and ZV_ON s<br>nals together can 3-state the ZV output pins and also<br>indicate, through ZV_ON, that the ZV port is isolated from<br>the L64014. |       |                             |   |    |  |

|   |     |     |      |                                                                                                                                                                                                                                                                                   | ,     | ne L64014 Z<br>BLE (pin 27) |   |    |  |

| Bit 6                                                                                                                                                                                                                                        | ZV ENABLE                                                                                                                                                                                                                                                | 71/ 01                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                                                                                                                                                                                                                                              | Input Signal                                                                                                                                                                                                                                             | ZV_ON<br>Output Signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ZV<br>Signal Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| 0                                                                                                                                                                                                                                            | 0                                                                                                                                                                                                                                                        | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | High Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| 0                                                                                                                                                                                                                                            | 1                                                                                                                                                                                                                                                        | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | High Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| 1                                                                                                                                                                                                                                            | 0                                                                                                                                                                                                                                                        | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | High Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| 1                                                                                                                                                                                                                                            | 1                                                                                                                                                                                                                                                        | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | High Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| 0                                                                                                                                                                                                                                            | 0                                                                                                                                                                                                                                                        | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | High Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| 0                                                                                                                                                                                                                                            | 1                                                                                                                                                                                                                                                        | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Active                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| 1                                                                                                                                                                                                                                            | 0                                                                                                                                                                                                                                                        | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Active                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| 1                                                                                                                                                                                                                                            | 1                                                                                                                                                                                                                                                        | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Active                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |