# Personal Logic Analyzer Incl. Options and Accessories PM 3632

Operating manual Edition 2.2

4822 871 80303 850218

Deutsche Uebersetzung eingeschlossen Avec traduction française

**PHILIPS**

A publication of:

Philips I & E

T & M - DTS Service Department.

Publication number 4822 871 80303

Copyright 1985, Philips Export B.V.

All rights strictly reserved. Reproduction or Issue to third parties in any form whatsoever is not permitted without written authority from the propietors.

Printed in the Netherlands.

# **CONTENTS**

| CHAPTER PAGE                               | Ε |

|--------------------------------------------|---|

| 1. INTRODUCTION                            |   |

| 1.1 GENERAL                                |   |

| 1.2 SYSTEM FAMILY                          |   |

| 1.3 SYSTEM SPECIFICATIONS                  |   |

| 1.3.1 PM 3632 LOGIC ANALYZER               |   |

| 1.3.2 OPTIONS AND ACCESSORIES 1-7          |   |

| 1.4 CONTROLS AND CONNECTIONS               | 1 |

| 1.4.1 FRONT PANEL FUNCTIONS                | 1 |

| 1.4.2 REAR PANEL FUNCTIONS                 | 3 |

| 1.5 AUDIBLE WARNINGS                       | 4 |

| A CONTROL TO THE CHARLE INDED THAT         |   |

| 2. CONNECTION TO THE SYSTEM UNDER TEST 2-1 |   |

| 2.1 GENERAL                                |   |

| 2.2 32-CHANNEL LOGIC POD                   |   |

| 2.3 4-CHANNEL FAST POD                     |   |

| 2.4 MICRO-PROCESSOR PODS                   |   |

| 2.5 STANDARD BUS POD                       |   |

| 2.6 ROM EMULATOR POD                       |   |

| 3. SET-UP SCREENS                          |   |

| 3.1 GENERAL                                |   |

| 3.2 SYSTEM STATUS SCREEN                   |   |

| 3.3 CLOCK SET-UP SCREEN                    |   |

| 3.4 CONFIGURATION SET-UP SCREEN            |   |

| 3.5 TRIGGER SET-UP SCREEN                  |   |

| 3.6 TRIGGER SEQUENCE SET-UP SCREEN         | 0 |

| 3.7 TRIGGER DELAY SET-UP SCREEN            | 4 |

| 3.8 FORMAT SET-UP SCREEN                   | 5 |

| 3.9 SPECIAL FUNCTIONS SET-UP SCREEN        | 8 |

| 4.1 G     | ENERAL      |        |     |          | •     |    |    |     |    |    |     |         |   |   |     |     | 4 - 1 |

|-----------|-------------|--------|-----|----------|-------|----|----|-----|----|----|-----|---------|---|---|-----|-----|-------|

| 4.1.1     | RECORDING   | DATA   |     |          |       |    |    |     |    |    |     |         |   |   |     |     | 4 - 1 |

| 4.1.2     | DISPLAYIN   | G DATA | ۸.  |          |       |    | •  |     | •  | ×  | ٠   | <b></b> | æ | • | +:- | *6  | 4 - 1 |

| 4.1.3     | MOVING TH   | E CURS | SOR | Al       | 4D    | s  | CR | 0 L | LI | NG | i . |         |   | : |     |     | 4 - 1 |

| 4.2 T     | IMING DISP  | _AY .  |     |          |       |    |    |     |    |    |     |         |   |   |     |     | 4-3   |

| 4.2.1     | INTRODUCT   | ON .   |     |          |       |    |    |     |    |    |     |         |   |   |     |     | 4 – 3 |

| 4.2.2     | MAGNIFIER   |        |     |          |       |    |    |     |    |    |     |         |   |   |     |     | 4 - 3 |

| 4.2.3     | TRIGGER L   | INE .  |     |          |       |    |    |     |    |    |     |         |   |   |     |     | 4~3   |

| 4.2.4     | TIME MEAS   | JREMEN | łΤ  |          | •     | •  |    |     |    |    |     |         |   |   |     |     | 4 - 4 |

| 4.2.5     | REFERENCE   | CURSO  | R   |          |       | •  |    |     |    |    |     |         |   |   |     |     | 4 - 4 |

| 4.2.6     | TIMING CH   | NNEL   | LA  | BEI      | L     | ΙN | G  |     |    |    |     |         |   |   |     |     | 4 - 4 |

| 4.3 L     | IST DISPLAY | ·      |     |          |       |    |    |     |    |    |     |         |   |   |     |     | 4 - 5 |

| 4.3.1     | INTRODUCT   | ON .   |     |          | . ,   |    |    |     |    |    | •   |         |   |   |     |     | 4 - 5 |

| 4.3.2     | MEMORY A    | OR B?  |     | <u>.</u> |       |    |    |     |    |    | •   | •       | • | * |     | ::• | 4 - 6 |

| 4.3.3     | LOGIC POD   | LIST   | 01  | SPL      | . A \ | ′  |    |     |    |    |     |         |   |   |     |     | 4 - 6 |

| 4.3.4     | MICROPROCE  | SSOR   | ΡO  | D L      | . I S | т  | D  | ΙS  | PL | ΑY |     |         |   |   |     |     | 4 - 6 |

| 4.4 01    | SASSEMBLY   | DISPL  | ΑY  |          |       |    |    |     |    |    |     |         |   |   |     |     | 4 - 8 |

| 4.4.1     | INTRODUCTI  | ON .   |     |          |       |    | ,  |     |    |    |     |         |   |   |     |     | 4 - 8 |

| 4.4.2     | STATE COLU  | IMN .  |     |          |       |    |    |     |    |    |     |         |   |   |     |     | 4 - 8 |

| 4.4.3     | PC COLUMN.  |        |     |          |       |    | ,  |     |    |    |     |         |   |   |     |     | 4 - 8 |

| 4 . 4 . 4 | DISASSEMBL  | Y COL  | UMI | Ν.       |       |    | ,  |     |    |    |     |         |   |   |     |     | 4 - 8 |

| 4.4.5     | BUS ACTIVI  | TY CO  | LUI | MN.      |       |    |    |     |    |    |     |         |   |   |     |     | 4 - 9 |

| 5. DE   | SCRIPTION OF THE PODS 5-1                 |   |

|---------|-------------------------------------------|---|

| 5.1 3   | 2-CHANNEL LOGIC POD PM 8860 5-1           |   |

| 5., 1,1 | INPUT PROBES 5-1                          |   |

| 5 1 2   | THRESHOLD VOLTAGE                         | ú |

| 5.1.3   | SET-UP                                    |   |

| 5.2 4   | -CHANNEL FAST POD PM 8862 5-2             |   |

| 5.2.1   | INPUT PROBES                              |   |

| 5.2.2   | THRESHOLD VOLTAGE                         |   |

| 5.2.3   | SET-UP                                    |   |

| 5.2.4   | GLITCH CAPTURE 5-2                        |   |

| 5.3 S   | TANDARD BUS POD PM 8863 5-3               |   |

| 5.3.1   | INTRODUCTION                              |   |

| 5.3.2   | MODES                                     |   |

| 5.3.3   | JUMPERING OPTIONS                         |   |

| 5.3.4   | REFRESH CYCLES                            |   |

| 5.3.5   | INTRQ* AND BUSRQ*                         |   |

| 5.3.6   | ASYNCHRONOUS OPERATION 5-5                |   |

| 5.4 8   | -BIT MICRO-PROCESSOR PODS PM 88658870 5-6 |   |

| 5.4.1   | GENERAL                                   |   |

| 5.4.2   | MICROPROCESSOR POD PM 8865 5-8            |   |

| 5.4.3   | MICROPROCESSOR POD PM 8866 5-9            |   |

| 5.4.4   | MICROPROCESSOR POD PM 8867 5-10           | 3 |

| 5.4.5   | MICROPROCESSOR POD PM 8868 5-1            | 1 |

| 5.4.6   | MICROPROCESSOR POD PM 8869 5-12           | 2 |

| 5.4.7   | MICROPROCESOOR POD PM 8870 5-13           | 3 |

| 5.5     | 16-BIT MICROPROCESSOR PODS 5-14           | + |

| 5.5.1   | GENERAL                                   | • |

| 5.5.2   | 68000/68010 POD PM 88745-15               | õ |

| 5.5.3   | 8086/8088 POD PM 8876 5-35                | 5 |

| 6. DESCRIPTIONS OF THE OPTIONS . ,                 | ) <del>-</del> 1 |

|----------------------------------------------------|------------------|

| 6.1 GENERAL                                        | 5-1              |

| 6.2 ROM EMULATOR POD PM 8864                       | S- 1             |

| 6.2.1 INTRODUCTION                                 | S - 1            |

| 6.2.2 CONNECTIONS TO THE PM 3632                   | 5-1              |

| 6.2.3 SETUP AND EDITING                            | 5-1              |

| 6.2.4 HARDWARE CONSIDERATIONS                      | 5 - 4            |

| 6.2.5 ERROR CODES                                  | 5 - 4            |

| 6.3 ROM EMULATOR MODULE PM 8880/00 8               | S - 5            |

| 6.4 RS-232C COMMUNICATION CARD PM 8880/20 8        | 5 - 5            |

| 6.4.1 GENERAL                                      | 3 - 5            |

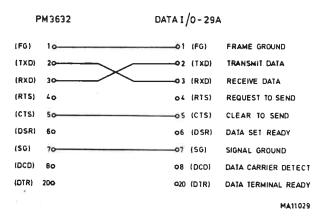

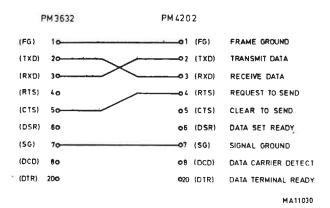

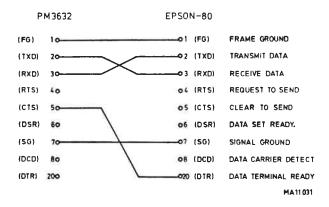

| 6.4.2 RS-232C OPERATING EXAMPLES AND CONNECTIONS 6 | 5 - 5            |

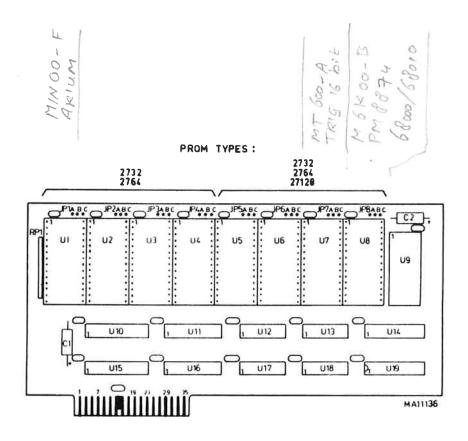

| 6.5 DISASSEMBLY ROM BOARD PM 8880/30 6             | 5-13             |

| 6.6 SET-UP (AND DATA) MEMORY PM 8880/40/50 8       | 5 - 14           |

| 6.6.1 INTRODUCTION                                 | 5-14             |

| 6.6.2 SET-UP MEMORY                                | 5-14             |

| 6.6.3 SET-UP AND DATA MEMORY                       | 5-14             |

| 6.6.4 INSTALLATION                                 | 5-15             |

| 6.6.5 OVERALL OPERATION                            | 5-15             |

| 6.6.6 SET-UP STORAGE                               | 5 - 15           |

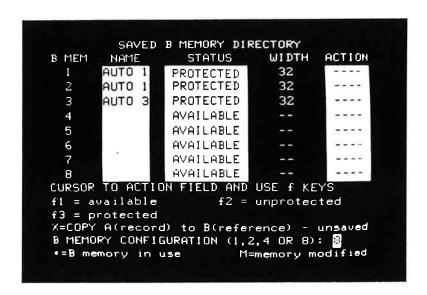

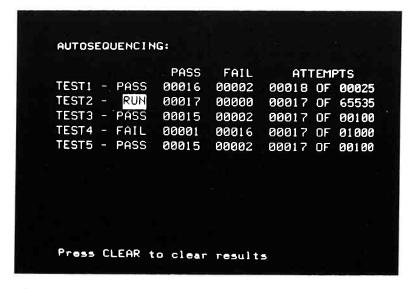

| 6.6.7 B MEMORY STORAGE                             | 5-19             |

| 6.6.8 COMPARING DATA                               | 5-23             |

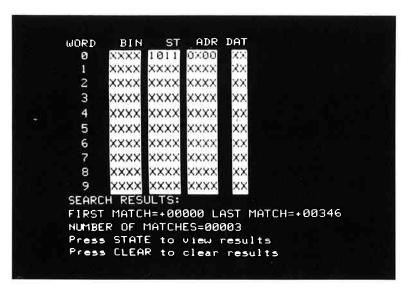

| 6.6.9 SEARCH                                       | -30              |

| 6.6.10 B MEMORY EDIT                               | i-32             |

| 6.6.11 A AND B MEMORY EXECUTION TIMES              | -33              |

| /. ]        | INSTALLATION INSTRUCTIONS | • | •  | •     | • | • | • | • | • | • | • | 7-1     |

|-------------|---------------------------|---|----|-------|---|---|---|---|---|---|---|---------|

| 7.1         | GENERAL                   |   |    |       |   |   |   |   |   |   |   | 7 - 1   |

| 7.2         | BUILDING-IN THE OPTIONS.  |   |    |       |   |   |   |   |   |   |   | 7-3     |

| 7.3         | PROM OVERVIEW             |   |    |       |   |   |   |   |   |   |   | 7 - 5   |

|             |                           |   |    |       |   |   |   |   |   |   |   |         |

| APPE        | NDICES                    |   |    |       |   |   |   |   |   |   |   |         |

| 1           | DISPLAY MESSAGES          |   |    |       |   |   |   |   |   |   |   | App-1   |

| 2           | ASCII-CODES               |   |    |       |   |   |   | , |   |   |   | App-5   |

| 3           | INTEL HEX FORMAT          |   |    |       |   |   |   |   |   |   |   | App-6   |

| 4           | B-MEMORY UPLOAD/DOWNLOAD  | F | RM | t A T | • |   |   |   |   |   |   | App-8   |

|             |                           |   |    |       |   |   |   |   |   |   |   |         |

| A T 17311 / | newrost Threv             |   |    |       |   |   |   |   |   |   |   | Alaba 1 |

## 1. INTRODUCTION

#### 1.1 GENERAL

The PM 3632 Logic Analyzer provides full-featured logic analysis for the debugging and troubleshooting of digital and micro-processor-based products, including complex triggering with list, timing, and (optionally) microprocessor disassembly displays.

Its basic function is to capture (record) the digital data on several signal lines, repetitively, and to do this synchonously or asynchronously with the clock of the system under test. High-speed, asynchronous operation is a powerful aid when solving hardware logic timing problems, while low-speed, synchronous operation is useful for debugging software.

The PM 3632 operates at speeds of up to 100 MHz, at data widths of up to 32 channels, and at a memory depth of up to 8000 samples per channel. At 100 MHz, the maximum number of channels is 4; when using 32 channels, the maximum speed is 12.5 MHz; and the maximum memory depth of 8000 samples per channel is available only when using up to 4 channels.

Data and clock qualifiers can be used, as well as trigger delay of up to 50,000 clocks. Data qualification is available only with 32-channel operation.

The optional ROM Emulator Module provides in-circuit emulation of 2716, 2732, 2764 and 27128 PROMs and immediate code patches, and an RS-232C interface provides for code downloading or uploading.

The PM 3632 contains a 5-inch, green-screen CRT which displays up to twelve channels of timing diagrams (with labelling) and has cursors for time-measurements.

The list display can be formatted and reformatted to achieve almost any conceivable digit combination in several number bases: ASCII, binary, octal, decimal, or hexadecimal.

Other options are micro-processor pods with one-clip connection to most popular micro-processors; the resulting disassembly display shows mnemonics for the various instruction and data sequences.

Four trigger words are available, and can be defined in binary, octal, decimal, or hexadecimal number base. These four words can be combined to form the trigger condition in many different ways. Nineteen trigger sequences are predefined and selectable, and the user may define his own sequence as well. All predefined sequences are available in the 32-channel mode, but these sequences are somewhat more limited in the other modes.

The PM 3632 has been designed for simple set-up and ease of operation. All set-up- and display screens contain complete prompting information which is self-explanatory for most situations. This enables the user to make productive use of this logic analyzer with a minimum of experience and, we hope, only infrequent reference to this manual.

The instrument has been designed and tested according to IEC Publication 348 for Class 1 instruments, and has been supplied in a safe condition. The present Operating Manual contains information and warnings which should be followed by the purchaser to ensure safe operation and to maintain the instrument in a safe condition.

#### 1.2 PM 3632 SYSTEM FAMILY

#### PODS

```

PM 8860

32-channel Logic Pod (standard accessory)

4-channel High-speed Pod

PM 8862

PM 8863

Standard Bus Pod

PM 8864

Rom Emulator Pod

Micro-processor Pod for 8085, 8031, 8032, 8035, 8039 and 8040

PM 8865

PM 8866

Micro-processor Pod for 6800, 6802 and 6808

PM 8867

Micro-processor Pod for 6809 and 6809E

PM 8868

Micro-processor Pod for 6502, 6512, 65002, 650102 and 650112

PM 8869

Micro-processor Pod for Z80 and Z80A/B/C

PM 8870

Micro-processor Pod for NSC800

PM 8874

Micro-processor Pod for 68000/68010

PM 8876

Micro-processor Pod for 8086/8088

```

Above specified Micro-processor Pods can be used for Disassembly.

#### OPTIONS

```

PM 8811 Serial Data Pod

PM 8880/00 Rom Emulator Module *

PM 8880/20 RS-232C Communication Card

PM 8880/30 Disassembly Rom Board

PM 8880/40 Set-up Memory

PM 8880/50 Set-up + Data Memory (can be used for data comparison)

PM 8880/80 Video Output Interface

PM 8883/00 System software rel. L

PM 8884/00 System software rel. L (french screen text)

```

- \* The PM 8880/00 Rom Emulator Module consists of:

- -PM 8864 Rom Emulator Unit Pod and

- -PM 8880/20 RS-232C Communication Card.

#### POD CONNECTING MATERIAL

```

PM 8882/10 8-channel Probe input wire set *

PM 8882/30 24-channel Probe input wire set *

PM 8882/50 Probe wire set (5 pieces) *

PM 8882/60 Test clip for 40-pin micro-processors

```

\* These sets have disconnectable test hooks

#### 1.3 SYSTEM SPECIFICATIONS

This specification applies to a PM 3632 Analyzer provided with standard Logic Pod PM 8860 unless otherwise stated.

Properties expressed in numerical values with stated tolerances are guaranteed for ambient temperatures of +5 deg.C...+40 deg.C unless stated otherwise.

Numerical values without tolerances are typical and represent the characteristics of an average instrument.

This specification is valid after the instrument has been switched-on for at least 15 minutes.

## 1.3.1 PM 3632 LOGIC ANALYZER

#### DATA INPUT

Input width : 4, 8, 16 or 32 bits.

The input width is also referred to as

number of channels.

Pod inputs

Sensitivity : + and -600 mV centered around threshold

Input voltage : + or -16 V (operating)

+ or -20 V (absolute rating)

Threshold : TTL or Variable

Variable ranges from +9 V to -9 V.

Input impedance : 100 kohm//6 pF

#### DATA RECORDING CLOCK

Internal (asynchronous)

Rate : 5 Hz...100 MHz

External (synchronous)

Data set-up time : 5 nsec max.

Data hold time : 1 nsec max.

Clock period : 14 nsec min.

Pulse width : 7 nsec min.

Clock edge : Positive or negative

(external clock only)

Clock qualifier : 1 (external clock only)

Qualifier input data same as for

the data inputs.

Max clock rate : Depending on the recording width, see

following list.

| Number of | Channels | Inte | rnal | Exter | nal |

|-----------|----------|------|------|-------|-----|

|           |          |      |      |       |     |

| 4         | 1        | 00   | MHz  | 70    | MHz |

| 8         |          | 50   | MHz  | 50    | MHz |

| 16        |          | 25   | MHz  | 25    | MHz |

| 32        |          | 12.5 | MHz  | 12.5  | MHz |

#### TRIGGERING

Trigger modes : Sequential or Combinational

Trigger words/events : Four

Trigger word width # 32 bits maximum (consistent with the

number of channels)

Selectable trigger sequences : 19 pre-defined and 1 user-defined.

Predefined : 0..9

A..F f1..f3

User-defined: f4

The number of trigger sequences being limited by the number of channels,

see following list:

| Number of Ch | annels Ava: | ilable  | Trigge  | r Sequences |

|--------------|-------------|---------|---------|-------------|

|              |             |         |         |             |

| 4            | 0,          | 1, 2,   | and 3   |             |

| 8            | 0,          | 1, 2,   | and 3   |             |

| 16           | 0,          | 1, and  | 1 4     |             |

| 32           | Al:         | l (incl | l. user | -defined)   |

Trigger Delay : 0...50,000 clock samples

DATA QUALIFICATION (32-bit mode only)

Qualification Modes : State and Combinational

State : Qualification words enable or disable data recording, thus blocks of data to be

recorded can be defined.

Combinational : Records only those words which:

1) match qualification words, or

2) don't match qualification words.

#### **MEMORY**

Memory depth

: Depending on the number of channels

| Number of | Channels | Recording | Oepth  | per | Channel |

|-----------|----------|-----------|--------|-----|---------|

|           |          |           |        |     |         |

| 4         |          | 8000      | sample | e s |         |

| 8         |          | 4000      | sample | s   |         |

| 16        |          | 2000      | sample | es  |         |

| 32        |          | 1000      | sample | es  |         |

#### LIST DISPLAY MODE

Word list

: 14 formatted words

Group columns

: 8 max

Number base

: Binary, octal, hexadecimal, decimal or ASCII

Repeatable in different number bases and

group columns.

Selectable bit groupings for each column.

#### TIMING DISPLAY MODE

Number of timing lines

on the display

: 12 max (any line may be repeated)

Cursors

: One main cursor, and one reference cursor.

Magnification (horizontal)

: x1 and

x10 (centered around main cursor)

Time measurements

Units

: Clock intervals.

-Clock periods with external clock -Time units with internal clock.

Measured time

Without reference cursor : Distance from trigger to cursor

With reference cursor : Distance from reference- to main cursor

#### DISASSEMBLY DISPLAY MODE

14-line list showing addresses, operands, data, mnemonics and bus activity.

## DATA SCROLLING

Continuous (auto repeat).

Absolute instantaneous cursor positioning at trigger.

Timing display mode

: Left/right shift, slow or fast

List- and disassembly

display modes

: Up/down Slow (one sample at a time), or

Fast (one screen at a time)

DISPLAY

5-inch, green phosphor CRT

MAINS INPUT

Voltage

: 220 or 240 V; internally adjustable.

(also adaptation to mains voltages of 100,

110, 120, 127, 200 or 250 V is possible)

Refer to chapter 7.

Frequency

: 50..60 Hz (not user-selectable)

Power consumption

: 170 W approx.

Mains fuse (in rear panel)

: 100-127V: 2 Amps (delayed)

200-250V: 1 Amp (delayed)

5x20 mm, glass tube (1 pc)

PHYSICAL MEASUREMENTS

Size

: Depth 38 cm

Width 30 cm

Heigth 13 cm

Weigth

: 9.9 kg

**ENVIRONMENTAL**

Temperature

: 0-40 deg C operating

Relative humidity

: 5-95%, non-condensing

## 1.3.2 OPTIONS AND ACCESSORIES

PM 8860 32-CH LOGIC POD

Data input

: Refer to PM 3632 system specification

Input PROBE 0-7

(16 wires)

: Channel 0...7 External clock Clock qualifier Six ground wires

Input PROBE 8-31

(26 wires)

: Channel 8...31 Two ground wires

Threshold voltage

: TTL = 1.4 V

VAR = -9...+9 V

The threshold voltage can be measured at point 19 of the PROBE 0-7 connector on the

Pod. Refer to Fig. 2.1

PM 8862 4-CH HIGH-SPEED POD

Clock frequency

: 100 MHz max, internal clock 75 MHz max. external clock

Threshold

: TTL = 1.4 V or,

VAR = -7.9...+7.9 V

The threshold voltage can be measured at the two-pole Molex connector connected to this Pod. The contact at the flat end of this connector is ground potential.

Input voltage

: -7.9...+7.9 V max.

Overdrive

: 40 mV

Input impedance

: 50 kohm// 6 pF

Set-up time

: 5 nsec

Hold time

: 0.5 nsec

Glitch capture

: selectable on/off

Minimum detectable glitch : 40 mV over threshold for 5 nsec.

#### PM 8863 STANDARD BUS POD

The STANDARD Bus Pod enables to capture bus cycles asynchronously (with the clock from the analyzer), or synchronously (with the external clock).

Modes : STDBUS STDINT STD24B

The STANDARD Bus Pod may be inserted into an unoccupied slot on the bus, or it may be used as an extender card.

#### PM 8864 ROM EMULATOR POD

For Rom Emulation the Analyzer must be provided with:

-PM 8864 Rom Emulator Pod and

-PM 8880/20 RS-232C Communication Card (located inside the Analyzer)

The ROM Emulator emulates one to four Read-Only Memories per Unit,

up to a total of 16 Kbytes of memory, and is configurable for 2716, 2732, 2764, or 27128 PROMs.

One or two PM 8864 pods may be used, for a total of 32 Kbytes of emulation memory. Two units can be daisy-chained.

The simulated ROM memory can be uploaded or downloaded, in several popular data transfer formats, to or from other equipment (such as computers/controllers or PROM programmers) via an RS-232C port on the back panel. The memory is then displayed on the PM 3632 screen and can be changed directly with front-panel key entries.

# PM 8865...8876 MICRO PROCESSOR PODS

These Pods provide one-clip connection to various micro-processors. These Pods must be used if a disassembler mode has been selected. The following Pods are currently available:

| Pod Type number | Micro-processors supported                    |

|-----------------|-----------------------------------------------|

| PM 8865         | Intel 8085, 8031, 8032, 8035, 8039 and 8040   |

| PM 8866         | Motorola 6800, 6802 and 6808                  |

| PM 8867         | Motorola 6809 and 6809E                       |

| PM 8868         | Rockwell 6502, 6512, 65C02, 65C102 and 65C112 |

| PM 8869         | Zilog Z80, Z80A, Z80B and Z80C                |

| PM 8870         | NSC800                                        |

| PM 8874         | 68000/68010                                   |

| PM 8876         | 8086/8088                                     |

Threshold: Fixed ITL

#### PM 8880/00 ROM EMULATOR MODULE

The PM 8880 Rom Emulator Module consists of:

-PM 8864 Rom Emulator Pod

-PM 8880/20 RS-232C Communication Card (located inside the Analyzer)

ROMs supported

: 2716, 2732, 2764 and 27128

ROM socket plugs

: 4 per Pod

Address bus (all ROMs)

: 14 lines, assumed common

Data busses

: 2

8-bits each, independent for 8- or 16-bits

targets.

Timing

1 Tacc : 200 nsec

Tce : 200 nsec

Toe : 70 nsec

Iol : 2.1 mA

Vol : 0.5 V

Data base interface

₽ RS-232C

Uploads/downloads in hex format

Data editing

From PM 3632 front-panel keys

## PM 8880/20 RS-232C COMMUNICATION CARD

Used in conjunction with the Rom Emulator for upload/download of emulation memory.

Other applications are

: Upload/Download system set-up files or reference memory contents, in conjunction

with the PM 8880/40/50.

#### PM 8880/30 DISASSEMBLER ROM BOARD

This board is required for disassembly of micro-processor programms, and can be installed inside the Analyzer.

For each Disassembler a specific Disa Prom must be present on this board. The Disa Prom is included in delivery with each Micro-processor Pod. Up to eight different Disa Proms can be located on the Disa Rom board.

#### PM 8880/40 SET-UP MEMORY

This unit exists of a non-volatile memory which can store upto eight complete system set-up files. Each file can be assigned a 6-character name and a status of 'protected' or 'unprotected'.

Set-up files can be uploaded or downloaded via the PM 8880/20 RS-232C communication Card.

This unit can be installed inside the Analyzer.

#### PM 8880/50 SET-UP AND DATA MEMORY

This unit exists of a non-volatile memory which can store upto eight complete system set-up files and one complete data memory (RAM) to be used as a reference memory.

The reference memory is referred to as the 'B'-memory. In relation to this the basic analyzer data memory is called the 'A'-memory.

The set-up files storage functions are described under 'Set-up Memory'. The reference memory can be partitioned into 1, 2, 4, or 8 equal segments. These segments can then be used by the various set-up files, either singly or in the automatic sequence mode. Each saved data segment can be assigned a 6-character name and a status 'protected' or 'unprotected'. Data segments can be uploaded or downloaded via the PM 8880/20 RS-232C Communication Card.

The unit can be installed inside the Analyzer.

#### 1.4 CONTROLS AND CONNECTIONS

#### 1.4. FRONT-PANEL FUNCTIONS

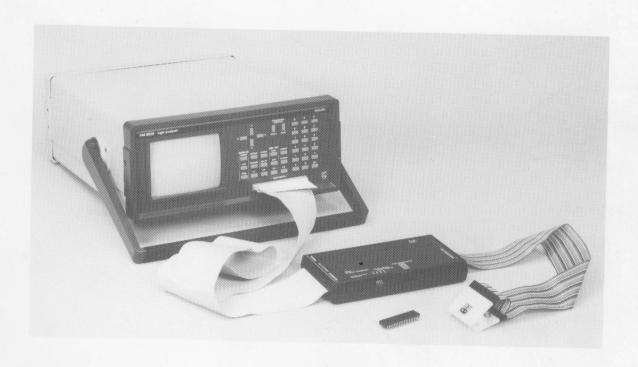

Fig. 1.1 PM 3632 Front Panel

INPUT CONNECTOR - For connecting the Pod.

WARNING: DO NOT PLUG OR UNPLUG THE POD CONNECTOR, WHILE THE UNIT IS POWERED UP.

All operating functions are controlled from the front-panel keybaord. All keys will repeat if held down; use a quick and sure touch to avoid unwanted repeating.

#### FOUR ARROW KEYS

To move the cursor on set-up screens, and to scroll through the data on display screens.

## START AND STOP KEYS

To start and stop data acquisition.

(To turn on the PM 3632, use the POWER Switch on the back panel).

### HEXADECIMAL KEYPAD

To set and change recording- and display parameters.

THREE DISPLAY KEYS (TIMING, LIST and DISASM) To select the data display mode.

#### EIGHT SET-UP KEYS

To access set-up screens for specifying parameters for data recording and data display formatting, including a special functions key.

#### FOUR FUNCTION KEYS of1 -- 4

Keys having various functions depending on the selected display, and on the position of the cursor.

#### CRT SCREEN

To display data and to set-up recording and display parameters. Any set-up screen may be accessed with only a single keystroke. Changeable fields are reverse-videoed and the cursor position blinks, the cursor automatically skips over nonchangeable fields.

To change any set-up or operating parameter, simply position the cursor over the selected field, then enter the desired parameter via the keypad. The new parameter (and any other value determined from it) will be updated and displayed. Actual update occurs when the screen or field is exited via the set-up keys or cursor.

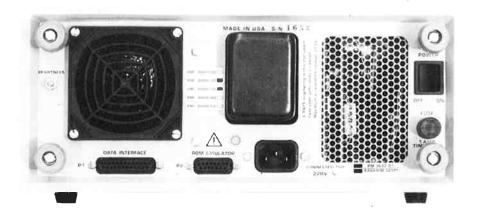

Fig. 1.2 PM 3632 Back Panel

From left to right:

BRIGHTNESS ADJUSTMENT Screwdriver control (with locking nut) for display intensity.

DATA INTERFACE CONNECTOR

RS-232C connection used for data uploading/downloading from a host

computer with the: Rom Emulator Module PM 8880/00

Set-up Memory PM 8880/40

Set-up/Data Memory PM 8880/50

ROM EMULATOR CONNECTOR

15-pin connector to connect the ROM Emulator Pod PM 8864

POWER SWITCH (ON/OFF)

MAINS FUSE:

110-127V : 2 Amps (delayed)

200-250V : 1 Amps (delayed)

5x20mm, glass tube

#### 1.5 AUDIBLE WARNINGS

#### -ONE BEEP

Warns that a wrong key has been depressed (including trying to move the cursor past the limits of the field or screen), and ignored by the system. For example, depressing a numerical key on a display screen will usually produce one beep.

Upon power-up, one beep verifies that the power is on.

#### -TWO BEEPS

Signal that data has stopped being recorded, i.e., that the trigger condition has occurred and that the trigger delay has been satisfied.

#### -THREE BEEPS

Warn that set-up entries are inconsistent, or that there are pod status errors. The screen will display an explanatory error message, such as:

- -"ALREADY STARTED" if the START key is depressed during data recording,

- -"POD CONNECTION ERROR" if the connection to the unit under test is wrong,

- -"NO DATA RECORDED" if the STOP key is depressed before any data has been recorded, etc.

#### -CONTINUOUS BEEPS

Indicate that a wrong key is being depressed continuously and is repeating.

# 2. CONNECTION TO THE SYSTEM UNDER TEST

## 2.1 GENERAL

Signals from the system under test are always applied to the Analyzer via a Pod.

Note that the analyzer configuration is automatically set according to the connected Pod.

## Input Pods

The Input Pods contain the necessary circuitry to adapt the signals of the system under test.

For detailed information on these Pods refer to chapter 5.

Four main Pod-versions are available:

- -A 32-channel Logic Pod.

This Pod is provided with separate probe input wires, and can be used for observation of, not only the microprocessor activity, but also for the signals in the asociated circuits.

- -A 4-channel 'FAST' Pod. This Pod features 100 MHz sampling, and selectable Glitch- or Non-glitch detection.

- -Micro-processor Pods. Various types are available corresponding to the most common micro-processors. These Pods are provided with a micro-processor test clip.

- -A Standard Bus Pod. This Pod features direct connection to a Standard Bus system backpanel.

#### Rom Emulator Pod

This Pod is used for emulation of the Rom Memory of the system under test. For detailed information refer to chapter 6.

## CONNECTION

To connect a Pod to the system under test:

- -Switch-off the mains voltage of the Analyzer.

- -Insert the Pod cable to the connector at the front panel of the Analyzer.

- -Connect the Pod probes or the microprocessorclip to the system under test.

- -Switch-on the Analyzer.

WARNING: DO NOT PLUG OR UNPLUG THE POD CONNECTOR, WHILE THE ANALYZER IS POWERED UP.

#### 2.2 32-CHANNEL LOGIC POD

The 32-channel Pod has 42 probes (16 on one probe set and 26 on the other probe set). Each probe input and ground is provided with an EZ hook clip.

The probe set with 16 wires is called the 8-Channel Probe Set; it contains Probes 0...7, the Clock Probe, the Clock Qualifier Probe and six grounds. This group is equipped for high-speed recording.

The probe set with 26 wires is called the 24-Channel Probe Set, and contains Probes 8-31 and two grounds.

Each probe has 3 parts: the tip (body) and the cap (plunger) of the EZ hook clip, and the wire; each part may be one of 10 colors.

#### Color coding:

- -Clock Probes have all three parts colored red.

- -Clock Qualifier Probes are all blue.

- -Ground Probes are all black

- -The remaining probes all have grey caps.

Refer also to the Color Coding list on the next page.

#### THRESHOLD VOLTAGE

The Pod contains a switch for selecting either "TTL" or "Variable" voltage threshold.

The "TTL" position sets the TTL level threshold voltage  $(1.4\ V)$ . The "Variable" position allows setting the threshold voltage between -9 V and +9 V by adjusting the potentiometer located next to the switch.

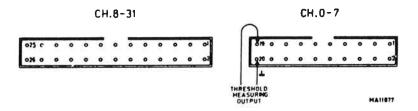

The threshold voltage can be measured at pin 19 on the pod's 20-pin connector, by using a high-impedance meter. The impedance of this node is about 1 Kohm. Pins 17, 18 or 20 can be used as measuring ground. Refer to Fig. 2.1.

## SET UP

Connect the desired number of probes (corresponding to the number of selected input channels) to the points on the circuit to be tested.

To sample data synchronously (external clock), connect the probe for the clock to the system under test.

The circuits of the input buffers for Clock, Clock Qualifier and Data channels 0--3 have been designed to be very fast, and care must be taken to minimize coupled noise.

#### WARNING

THE CLOCK AND CLOCK QUALIFIER WIRES SHOULD ALWAYS BE TWISTED WITH A CONNECTED GROUND LEAD. FOR OPERATION ABOVE 10 MHz, THE LOWER DATA CHANNELS SHOULD ALSO BE TWISTED WITH THE GROUND LEADS PROVIDED.

# PROBE SET COLOR CODING

# 8-Channel probe set

| Signal    | Body (tip)   | Plunger (cap) | Wire        | Pod Connector Pin |

|-----------|--------------|---------------|-------------|-------------------|

|           |              |               |             |                   |

| Probe 0   | Black        | Grey          | Black       | 2                 |

| Probe 1   | Black        | Grey          | Brown       | 3                 |

| Probe 2   | Black        | Grey          | Red         | 5                 |

| Probe 3   | <b>Black</b> | Grey          | Orange      | 6                 |

| Probe 4   | Black        | Grey          | Yellow      | 8                 |

| Probe 5   | Black        | Grey          | Green       | 9                 |

| Probe 6   | Black        | Grey          | Blue        | 11                |

| Probe 7   | Black        | Grey          | Violet      | 12                |

| Clock     | Red          | Red           | Red         | 16                |

| Qualifier | Blue         | Blue          | Blue        | 14                |

| Grounds   | Black        | Black         | Black       | 1/4/7/10/13/15    |

| Threshold | -            | -             | .7.         | 19                |

| Ground    | -            | -             | <b>26</b> 3 | 20                |

# 24-Channel probe set

| Signal   |        |       |        | Pod Connector Pin |

|----------|--------|-------|--------|-------------------|

|          |        |       |        |                   |

| Probe 8  | Black  | Grey  | Grey   | 2                 |

| Probe 9  | Black  | Grey  | White  | 3                 |

| Probe 10 | Brown  | Grey  | Black  | 4                 |

| Probe 11 | Brown  | Grey  | Brown  | 5                 |

| Probe 12 | Brown  | Grey  | Red    | 6                 |

| Probe 13 | Brown  | Grey  | Orange | 7                 |

| Probe 14 | Brown  | Grey  | Yellow | 8                 |

| Probe 15 | Brown  | Grey  | Green  | 9                 |

|          |        |       |        |                   |

| Probe 16 | Brown  | Grey  | Blue   | 10                |

| Probe 17 | Brown  | Grey  | Violet | 1 1               |

| Probe 18 | Brown  | Grey  | Grey   | 1 2               |

| Probe 19 | Brown  | Grey  | White  | 13                |

| Probe 20 | Red    | Grey  | Black  | 15                |

| Probe 21 | Red    | Grey  | Brown  | 16                |

| Probe 22 | Red    | Grey  | Red    | 17                |

| Probe 23 | Red    | Grey  | Orange | 18                |

|          |        | -     |        |                   |

| Probe 24 | Red    | Grey  | Yellow | 19                |

| Probe 25 | Red    | Grey  | Green  | 20                |

| Probe 26 | Red    | Grey  | Blue   | 21                |

| Probe 27 | Red    | Grey  | Violet | 22                |

| Probe 28 | Red    | Grey  | Grey   | 23                |

| Probe 29 | Red    | Grey  | White  | 24                |

| Probe 30 | Orange | Grey  | Black  | 25                |

| Probe 31 | Orange | Grey  | Brown  | 26                |

|          |        |       |        |                   |

| Grounds  | Black  | Black | Black  | 1/14              |

Fig. 2.1 Connector pin numbering on the 32-channel Pod (as seen on the Pod)

#### 2.3 4-CHANNEL FAST POD

WARNING: DO NOT PLUG OR UNPLUG THE POD CONNECTOR, WHILE THE ANALYZER IS POWERED UP.

-- .. .

This Pod has 6 twisted wire input pairs terminated in EZ Hook clips. Each signal lead has a resistor in the lead adjacent to the clip, to reduce signal reflection.

#### INPUT COLOR CODING

|                | EZ Hooks  |              |  |  |  |  |

|----------------|-----------|--------------|--|--|--|--|

| Signal         | Body(tip) | Plunger(cap) |  |  |  |  |

| Channel 0      | Grey      | Black        |  |  |  |  |

| Channel 1      | Grey      | Brown        |  |  |  |  |

| Channel 2      | Grey      | Red          |  |  |  |  |

| Channel 3      | Grey      | Orange -     |  |  |  |  |

| External clock | Red       | Red          |  |  |  |  |

| Qualifier      | Blue      | <b>Blue</b>  |  |  |  |  |

| Grounds        | Black     | Black        |  |  |  |  |

#### THRESHOLD VOLTAGE

This Pod contains a switch to select either "TTL" or "Variable" voltage threshold.

The "TTL" position (switch away from the screwdriver slot) sets the TTL level threshold voltage (1.4 V).

The "Variable" position (switch towards the screwdriver slot) allows setting the threshold voltage between -7.9 V and +7.9 V by adjusting the potentiometer located next to the switch.

Provision is made for measuring the threshold voltage by a pair of wires on the probe set which terminates in a 2-pole connector. The threshold voltage may be measured here with the contact on the flat end of the connector being at ground.

Use a high-impedance meter; the impedance of this node is about 1 kohm.

## SET UP

To sample data synchronuously with an external clock, connect probes for the clock and (optionally) the clock qualifier to the circuit. The input buffers for Clock, Clock Qualifier, and Data channels 0-3 have been designed to be very fast, and care must be taken to minimize coupled noise.

NOTE: THE CLOCK AND CLOCK QUALIFIER WIRES SHOULD ALWAYS BE TWISTED WITH A CONNECTED GROUND LEAD. FOR OPERATION ABOVE 10 MHz, THE LOWER DATA CHANNELS SHOULD ALSO BE TWISTED WITH THE GROUND LEADS PROVIDED.

THE ALL BLACK EZ HOOKS ARE THE GROUND CLIPS, AND SHOULD BE CONNECTED TO A CIRCUIT GROUND CLOSE TO THE SIGNAL BEING OBSERVED.

THIS POD CONTAINS SEVERAL HIGH-SPEED INTEGRATED CIRCUITS, WHICH DISSIPATE A LARGE AMOUNT OF HEAT. DO NOT USE IT IN ANY POSITION WHICH OBSTRUCTS THE NORMAL AIRFLOW AROUND IT.

#### 2.4 MICRO-PROCESSOR PODS

WARNING: DO NOT PLUG OR UNPLUG THE POD CONNECTOR,

WHILE THE ANALYZER IS POWERED UP.

To connect a micro-processor Pod, insert its cable connector plug into the connector on the front panel, then clip the probe to the micro-processor.

The brown wire on the colored ribbon cable must connect to Pin 1 of the micro-processor (this must correspond with the '1' indication on the Pod near the connector of the microprocessor clip ribbon cable). Information obtained internally from this Pod will determine some of the PM 3632 set-up parameters.

Refer to chapters 5.4 and 5.5.

#### 2.5 STANDARD BUS POD

WARNING: DO NOT PLUG OR UNPLUG THE POD CONNECTOR, WHILE THE ANALYZER IS POWERED UP.

The STANDARD Bus Pod consists of a p.c. extender board and a cable for connection to the PM 3632.

To connect the STANDARD Bus Pod, attach its cable connector plug to the connector on the front panel. Insert the circuit card into an unused slot in the STANDARD bus backplane of the unit under test, or install it as an extender between the bus and a card on the bus. For detailed information refer to chapter 5.

## 2.6 ROM EMULATOR POD

WARNING: DO NOT PLUG OR UNPLUG THE CONNECTOR, WHILE THE ANALYZER IS POWERED UP.

To connect the ROM Emulator Pod, insert the module's connector into the ROM EMULATOR connector receptacle on the back panel. Then plug the proper DIL plug directly into the ROM sockets of the system under test. For detailed information refer to chapter 6.

## 3. SET-UP SCREENS (MENUS)

#### 3.1 GENERAL

To set up the PM 3632 for operation, use the front-panel set-up keys: CLOCK, CONFIG, TRIG, SEQ, DELAY and FORMAT.

Each of these keys calls up a CRT screen offering parameter selections and/or set-up information. Changeable fields on the CRT display are reverse-videoed and the cursor position blinks; the cursor automatically skips over non-changeable fields.

The STATUS key selects the STATUS display which contains the main status parameters. There are no changeable fields in this display.

Each screen contains complete prompting information about how to set-up each parameter, including exactly what the preset options are, the specific key designated to select each option, and the allowable ranges of parameter values.

Also, the system protects against most wrong entries and selections, by not accepting them, and beeping to warn the user.

As soon as a parameter has been set, any other parameter dependent upon it is updated and displayed, usually immediately. In some cases, a dependent parameter is not updated until the cursor has left the field of the parameter being changed.

To select or change any set-up or display parameter, simply move the cursor to the parameter's field, which will cause it to blink, indicating its readiness to be set up.

Each parameter may be set in one of two ways:

- -A limited number (usually 2 or 3) of preset options, entered via the function keys f1--f4.

- -The actual value of a parameter (usually numeric) entered via the hexadecimal keys (0--F), including the "X" (don't care)- and the CLEAR key.

While the PM 3632 is recording, a blinking "ACTIVE" message is displayed in the upper right of the six set-up screens; during this time, set-up parameters may be viewed on each screen, but not changed.

## Note:

To change a parameter on any set-up screen, recording must first be stopped (by depressing "STOP").

#### 3.2 SYSTEM STATUS SET-UP SCREEN

To view overall major system parameters, depress the STATUS key on the front panel.

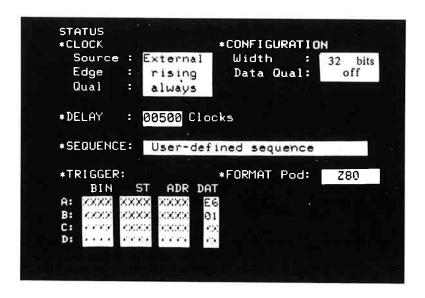

Fig. 3.1 System Status set-up screen after power-on.

To view system parameters in greater detail than is shown on the System Status set-up screen, to set up the PM 3632 for initial operation, and/or to change any detailed system parameters while using the PM 3632, use the following set-up keys on the front panel:

CLOCK (Recording/sampling rate and clock qualification)

CONFIG (Recording width/number of channels and data (Configuration) qualification)

TRIG (Trigger) (Triggering condition, which stops the recording process)

DELAY (Trigger Delay)

FORMAT (Data display format)

(or use default format)

Refer to Figure 3.1 System Status Set-up Screen, as an example of how one particular set of selections will be displayed.

## NOTE:

Labels which are preceded by asterisks refer to keys which access those parameters.

Following are the system parameters as they are displayed on the System Status screen and the selections for each parameter which are available to the user.

## CLOCK

Source : Internal

Period: .... nsec (4-digit numerical value and units)

or, Source : External

Sense : rising or falling (Edge)

Qual : Always, Low or High (Clock qualification)

## CONFIGURATION

Width : 32, 16, 8 or 4 bits

Data Qual : Off

or,

Width : 32, 16, 8 or 4 bits

Data Qual : Comb.

Record : Only or All but

Occur. of : None or ..... (Trigger words)

or,

Width : 32, 16, 8 or 4 bits

Data Qual : State

Enable : None or ..... (Trigger words)

Disable : None or ..... (Trigger words)

## TRIGGER DELAY

\*DELAY : ..... Clocks (5-digit value; default =00000)

#### TRIGGER \*SEQUENCE : .....

Displays the sequence from the 19 possible sequences as shown in the Trigger Sequence screen see Figure 3.5.

## \*TRIGGER:

A: .....

B: .....

C: .....

D: .....

Displays the selected trigger words in number base and the selected or default (List) display format. Default is all "Xs".

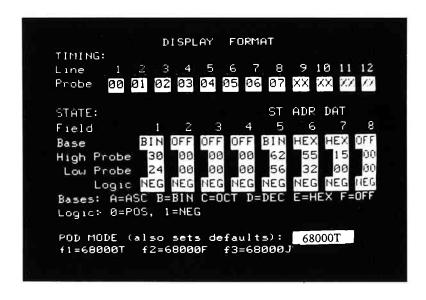

\*FORMAT Pod: ..... (mode)

Most pods have more than one mode, in which case the f1, f2, f3 or f4 key is used to select the particular mode via the Display Format set-up screen: e.g., the f1 key would select the 8085 mode of the PM 8865 micro-processor pod.

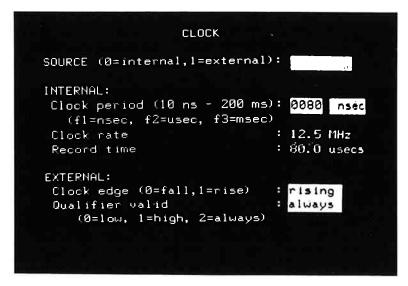

#### 3.3 CLOCK SET-UP SCREEN

To call up the Clock set-up screen, depress the CLOCK key. This screen displays the internal and external clocking parameters and is used to select and change specific parameters.

Fig. 3.2 Clock Set-up Screen after Power-up

#### SELECTING THE CLOCK SOURCE

The internal clock (generated by the Analyzer itself) is used when analyzing problems related to logic, hardware and timing, and when measuring time. (Asynchronous clock). Generally the internal clock is set to a frequency much higher than the clock of the system under test.

The external clock (taken from the system under test) is used for analyzing bus problems ,software and occurences synchronous to the system under test. (Synchronous clock).

External clock rates may not exceed 70 MHz (4-bit mode). For rate limits in other modes, refer to chapter 1.3 'System Specifications'.

To select (clock) Source, move the cursor to the field labeled "Source", then select either "Internal" by depressing the 0 key on the keypad, or "External" by depressing the 1 key on the keypad. The internal clock uses time periods in nanoseconds (nsec), microseconds (usec), or milliseconds (msec).

## USING THE INTERNAL CLOCK

To set the clock period (from 10 nsec to 200 msec), move the cursor to the first field to the right of "Clock period" and enter the desired value via the hexadecimal keypad. Then move the cursor to the second field and press one of the three preset options for units by depressing f1, f2, or f3.

The corresponding clock (recording) rate, or frequency, and record time will be automatically displayed as soon as the cursor leaves the Clock Period numerical field.

- 3 - 4 -

Not every frequency is available. When an unavailable selection is made, the closest available clock frequency will be automatically selected.

#### USING AN EXTERNAL CLOCK

The external clock is generally taken from the system under test. The clock detection circuitry of both the PM 8860 and the PM 8862 is very high speed.

To avoid extra clocks due to stray pickup, a connected ground lead should always be twisted with the clock lead. The PM 8862 leads are twisted pairs, but the PM 8860 leads are not.

Failure to twist a connected ground lead with the clock lead is likely to produce extra ("double") clocking; if these clocks occur at a period of less than the minimum, the Analyzer may function incorrectly.

#### NOTE

Because of the PM 3632's internal configuration, a minimum of 17 clocks must occur after the trigger condition for correct operation. These 17 clocks are automatically accounted for in all displays; the user need not be concerned about them unless the external clock stops within 17 clocks of the trigger event.

## Clock Edge

To select the Clock Edge (the edge of the clock at which data is to be sampled), depress the O key for "Falling" or the 1 key for "Rising". "Falling" means that the data is sampled on the high-voltage-to-low-voltage transition of the external clock input, as it crosses the threshold voltage; "Rising" means that data is sampled on the upward transition.

## Clock Qualifier

To select the clock qualifier, depress 0 (Low), 1 (High), or 2 (Always) on the keypad. "Low" means that the qualifier is valid only when the qualifier input is low; and "Always" means that the qualifier is always valid (don't care). External clocks are recognized only when the qualifier is valid.

#### NOTE.

The clock qualifier has no effect with the internal clock.

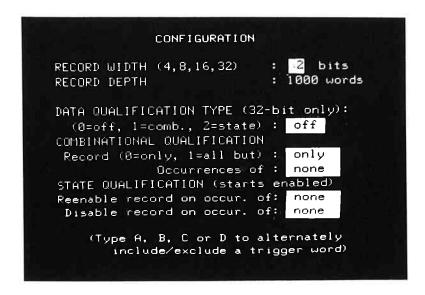

#### 3.4 CONFIGURATION SET-UP SCREEN

To call up the Configuration set-up screen, depress the CONFIG key.

Fig. 3.3 Configuration Set-up Screen

This screen shows information about the Record Width related to the Record Depth, and the Data Qualification parameters.

## RECORD WIDTH

To select the Record Width, move the cursor to the field labelled "Record Width" and enter the number of bits (channels) (4, 8, 16, or 32), on the keypad. If any other value is entered, it will not be accepted, and the next highest of these four values will be displayed.

The record depth (available memory) will then be automatically displayed. A higher number of channels has less record depth; e.g., 8000 samples per channel will be recorded in the 4-channel mode, and 1000 samples per channel in the 32-bit mode).

The maximum clock rate (speed) for each record width varies from 100~MHz (for 4-bit) to 12.5~MHz (for 32-bit).

The following tabel shows the relationships between record width, clock rate (speed), and record depth.

| Record |      | width |        | Max. clo | ck freq. | Recor | Record depth  |  |

|--------|------|-------|--------|----------|----------|-------|---------------|--|

|        |      |       |        |          |          |       |               |  |

| 4      | bits | (int. | clock) | 100      | MHz      | 8000  | samples/words |  |

| 4      | bits | (ext. | clock) | 70       | MHz      | 8000  | samples/words |  |

| 8      | bits |       |        | 50       | MHz      | 4000  | samples/words |  |

| 16     | bits |       |        | 25       | MHz      | 2000  | samples/words |  |

| 32     | bits |       |        | 12.5     | MHz      | 1000  | samples/words |  |

## DATA QUALIFICATION (in the 32-bit mode only)

Data qualification is used to record only desired pieces of data (blocks), to conserve memory, and to make problem areas more visible. It permits determination on an individual (combinational) or sequential (list) basis as to whether or not any given word (data sample) will be recorded. It is available in 32-channel mode only.

Note that data qualification does not affect recognition of trigger words, but does affect the trigger delay; i.e., a word included in the trigger sequence will be recognized regardless of whether or not data qualification allows it to be recorded, but only qualified words are counted in the trigger delay.

To select the type of Data Qualification, enter a 0 (Off), a 1 (Combinational), or a 2 (State) via the keypad.

To select the trigger words to be used as data qualifiers, use the A...D keys. When more than one word is entered, the display will automatically show a "+" between the words, meaning "or". Each A...D key toggles on/off when depressed repeatedly, causing the character to alternately appear and disappear.

# Combinational Data Qualification

To select a combinational data qualifier, depress 0 (only) or 1 (All but) in the field labeled "Record", then enter A, B, C and/or D in the "Occurrence of" field to indicate the trigger words upon which the selected qualifier will act. All four trigger words (A...D) may be used. Setting of trigger words is described in chapter 3.5.

For example, to record only program fetches in the area of 0100H to 02FFH when using a micro-processor pod, proceed as follows:

- -Set the trigger Word C to fetches with the Address field D1XX and the Data field XX.

- -Set the trigger word similarly, with 02XX in the Address field.

- -Set Data Qualification Type to "Comb"

- -Set "Record" under Combinational Qualification to "only"

- -Set "Occurences of" to "C+D".

## State Data Qualification

To select a state data qualifier, enter the selected trigger conditions upon which recording will be enabled or disabled in the appropriate fields Recording always begins when the START key is depressed.

Only one or two trigger words per field may be used; although the field is large enough to enter three or four words, the logic analyzer will not start recording data if more than two have been entered.

## NOTE :

When state data qualification is being used, trigger word "D" is not available for trigger sequence and, if either field ("Reenable .." or "Disable ..") contains two words, then trigger word "C" is also unavailable for trigger sequence. (It is convenient to use "C+D" for data qualification, so as to leave A and B open for triggering). For example, with state qualification, to record everything from the time an instruction is fetched at 3F27H until an instruction is fetched at 4010H, set trigger words C and D to fetches at those locations, enable state qualification, and set "Reenable .." to C and "Disable .." to D.

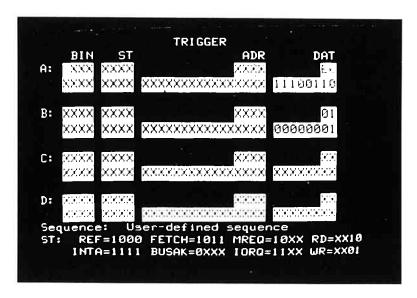

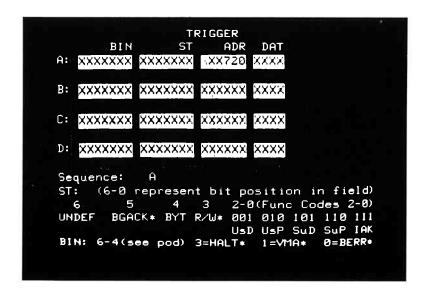

#### 3.5 TRIGGER SET-UP SCREEN

The TRIG key calls up the Trigger set-up screen with which four trigger words (events), labeled "A", "B", "C", and "D", are displayed and defined.

Fig. 3.4 Trigger Set-up Screen

On the display, there are two lines per trigger word. The first line shows the trigger word in the number base as selected in the Format screen (not in ASCII). The second line always shows the trigger word in binary. There is no separate field for the trigger format.

Fields are displayed from left to right, in ascending numerical order; "off" fields are not displayed. All numbers are displayed with the least sufficient digit at the right of the field; for binary fields, this means Bit 0 is at the right of the field.

To define a trigger word, move the cursor to either (first or second) line and use the keypad to enter the appropriate value.

The value on the other line will be changed accordingly.

To change any character in a trigger word, just move the cursor to the appropriate position, and enter the character via the keypad.

With the 32-ch. logic pod, the default number base for the upper line is binary, and is so labeled on the screen.

With micro-processor and bus pods, the default number base is hex for many fields, but is determined by the particular pod and its requirements. Micro-processor pods also label fields as "STS" (status bits), "ADR" (address), and "DAT" (data).

An attempt to enter a value which is too large for the selected number base will be rejected, and will cause the unit to beep once as an error warning.

In decimal number base, as further protection against entering unacceptable values, the PM 3632 will truncate the upper bits of a value that is larger than allowed: e.g. in decimal number base, if "18" is entered in a 4-bit field, as soon as the cursor leaves the field, the "18" is truncated to "2", an acceptable value).

To change the number base from the default or previously set base, use the Display Format screen via the FORMAT key. Refer to Chapter 3.8.

To indicate a "Don't Care" when entering a trigger word on either line, depress "X" on the keypad. Any resulting indeterminate character on the upper line will be displayed as a "?". In decimal number base, a "Don't Care" may not be entered for an individual digit because of the binary nature of the unit.

The bottom two lines of this set-up screen may contain information about the status fields. The presence of such information depends upon which micro-processor pod is being used and whether the appropriate disassembler has been installed in the PM 3632. Possible status code prompts are:

| FETCH | Instruction fetch (first byte of an instruction) |

|-------|--------------------------------------------------|

| MRD   | Memory read                                      |

| MWR   | Memory write                                     |

| HLDA  | Hold acknowledge                                 |

| INTA  | Interrupt acknowledgement                        |

| IORD  | I/O read                                         |

| IOWR  | I/O write                                        |

|       |                                                  |

See chapter 5.4, Micro-processor Pods, for further details of the status codes.

Figure 3.4 shows four trigger words defined to be matched with any type of access (fetch, read, write, etc.) to one of four addresses. In all four cases shown, the trigger condition is satisfied no matter what data is transferred during that cycle (Data is don't cares).

#### 3.6 TRIGGER SEQUENCE SET-UP SCREEN

The Trigger sequence screen is shown after pressing the SEQ key. The trigger sequence defines the trigger condition which will stop the recording of data after the selected trigger delay. If the delay is zero, recording stops immediately upon occurrence of the trigger condition.

```

TRIGGER SEQUENCE: ('+' means 'or')

7: A then B then C

0: A

1: A+B

8: (A+B) then (C+D)

2: A+B+C

9: (A+B+C) then D

3: A+B+C+D

A: A then (B+C+D)

4: A then B

B: (A+B) then C then D

5: (A+B) then C

C: A then (B+C) then D

6: A then (B+C)

D: A then B then (C+D)

E: A then B then C then D

F: A then (B without C)

fl: A then B then (C without D)

f2: (A+B) then (C without D)

f3: A then (B without C) then D

f4: User-defined sequence

```

Fig. 3.5 Trigger Sequence Set-up Screen

A trigger sequence condition is formed by various combinations or sequences of the selected trigger words (events), up to four words (labeled A, B, C and D) and four levels. Trigger words are defined via the Trigger set-up screen. Refer to chapter 3.5.

The Trigger Sequence set-up screen is used to select (and to change the selection of) any of the pre-defined trigger sequences, and to access (via the f4 key) the User-Defined Sequence set-up screen.

## PRE-DEFINED TRIGGER SEQUENCES

The Trigger sequence screen is shown after pressing of the TRIG key. This screen displays the 19 pre-defined trigger sequences, which are listed in Figure 3.5, along with the corresponding keypad entries for selecting them.

To select a pre-defined trigger sequence, depress the key which corresponds to the selected sequence; it will then be displayed on the second line of the screen, and may be changed via the keypad.

"O" (predefined as "A") is the default setting.

Other selections include combinations or sequences of trigger words (events) to make up the trigger condition. E.g., the sequence designated "7" ("A then B then C") will cause recording to continue until trigger word "A" is encountered, then until trigger word "B" is encountered, then until triggerword "C" is encountered. At this point, the entire trigger condition has been satisfied, and the delay will begin. Recording will stop immediately if the delay is zero.

Sequence f1 ("A then B then (C without D)") is identical to Sequence 7, except that, if "D" is encountered after "B" but before "C", then the PM 3632 will begin again to search for "A".

This sequence can be very useful when it is desired to trigger only when one event occurs immediately after another. To do this, use a sequence such as the f1 sequence, with "D" containing all "Don't Cares": in this case, "B" and "C" will have to occur with no other cycles in between to satisfy the trigger condition.

Only in the 32-channel operation are all 19 trigger sequences (including the user-defined sequence) available, as shown in the table below.

| Record wid | ith | Availabl | e Tri  | gger s | equences    |    |

|------------|-----|----------|--------|--------|-------------|----|

|            |     |          |        |        |             | -  |

| 4 channel  | Ls  | 0,       | 1, 2,  | and 3  |             |    |

| 8 channe   | Ls  | 0,       | 1, 2,  | and 3  |             |    |

| 16 channel | Ls  | 0,       | 1, and | d 4    |             |    |

| 32 channe? | Ls  | A11      | (inc   | luding | user-define | d) |

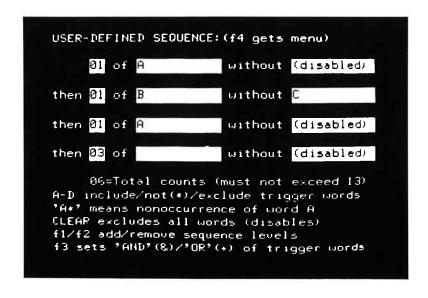

### USER-DEFINED TRIGGER SEQUENCE

To select or change the user-defined trigger sequence, first depress the f4 key, which brings up a new screen ("User-Defined Sequence") and presents a complex sequence format with one to four levels.

Fig. 3.6 User-defined Sequence Set-up Screen

Each level displays three fields: a 2-digit field for number of counts for that level, an 11-character field for a trigger word combination, and a second 11-character field for a "without" trigger word combination. When recording, the PM 3632 waits at each level until that condition has been satisfied.

If the entered count for a level is greater than one, then that level must be satisfied that number of times before the PM 3632 proceeds to the next level. If the "without" condition is encountered at a level, then the whole sequence starts over at the first level.

The screen's default format displays only the first trigger sequence level. To add a level, depress the f1 key; to remove the lowest level, depress the f2 key.

To enter the number of counts for each level, enter the value via the keypad. Up to 13 total counts (among all four levels) are allowed; e.g., if a total of 9 counts has been entered into the first three levels, then no more than 4 counts may be entered into the fourth level. After entry of the number of counts for a level, the new total number of counts is displayed as soon as the cursor is moved. Any level whose count is greater than 13 will be limited to 13 if its count field is exited. If the new total number of counts exceeds 13, any attempt to leave the screen vauses the PM 3632 to beep 3 times, flashes the "must not exceed 13" message, and does not allow leaving the screen.

To enter the trigger word combinations for each level, use the keypad to enter the desired combination of available trigger words ("A", "B", "C", and "D").

To include a trigger word, depress the key quickly and surely, do not linger on the key or it will repeat and change the entry.

If a word has already been entered in the field, the new word will be entered as an "or" word (shown as "+") or as an "and" word (shown as "&"), depending upon the mode. E.g., in the "or" mode, if "A" is already in the field, depressing the B key will enter "+B", and the field will show "A+B", meaning "A or B".

To change an entered trigger word to a "not" condition, depress the same key a second time (with the cursor in the appropriate field), and the display will place a "\*" ("not").

E.g., if "A+B" is already in the field, depressing the B key will add an asterisk to the "B", and the field will show "A+B\*", meaning "A or not B".

To exclude an entered trigger word, depress the same key a third time and the word (and its attached asterisk) will disappear from the field display. If the word was not a negative, i.e., had no asterisk, the key must be depressed twice toggling through the negative condition to get to the excluded one.

Depressing the same key a fourth time will toggle back to include the trigger word, etc., repeating the pattern of inclusion/negation/exclusion endlessly.

To change (all of) the "+" ("or") characters in the trigger word to "&" ("and"), depress the f3 key; depressing f3 again toggles all the "&" characters back to "+" characters, in another repeating pattern.

To exclude (erase) an entire trigger word sequence from a field, depress CLEAR, and the display will show "(disabled)" is the field.

To return to the Trigger Sequence set-up screen, depress the f4 key, which toggles the display back and forth between the Trigger Sequence and the User-Defined Sequence set-up screens.

#### NOTE :

When setting a user-defined sequence, be sure to exit from the User-Defined Sequence set-up screen directly to any screen <u>except</u> the Trigger Sequence set-up screen. Exiting from the User-Defined Sequence set-up screen directly to the Trigger Sequence set-up screen will reset the Trigger Sequence to its default condition (Sequence 0, which is "A"); the user-defined sequence will be remembered, but will not be used to trigger the analyzer.

To collect data without the possibility of a trigger condition stopping the recording of data (i.g., to collect data indefinitely until the STOP key is depressed), set the user-defined trigger sequence to exclude all trigger words by entering "01" as the number of counts, then depressing CLEAR to enter "disabled" in both trigger word fields. The display will then show "0 of (disabled) without (disabled)". This works only in the 32-channel mode.

#### NOTE :

Entering a number in the second field is only an alternate means of setting the trigger delay (the delay from the trigger event until stopping of the recording process). Trigger delay forces a number of data words to be stored after the trigger event. It cannot, however, guarantee the number of words before the trigger event.

For example, if the trigger condition is satisfied on the tenth clock, there will be only ten data words prior to the trigger.

Sometimes this makes it difficult to capture the beginning of a software loop. This can be overcome by triggering on a second occurrence of a particular event.

For example, trigger word "A+B" could be set to the same thing and a sequence of "A then B" set into the machine.

Alternatively, a user-defined sequence of 13 occurrences of A would cause a minimum of 12 full copies of the loop in memory prior to the trigger event.

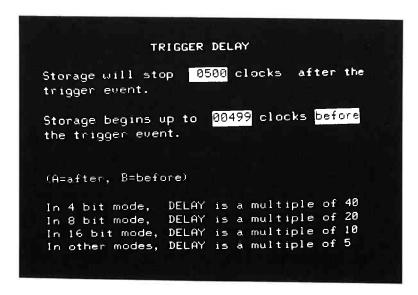

#### 3.7 TRIGGER DELAY SET-UP SCREEN

The Trigger Delay set-up screen is shown after pressing the DELAY key.

Fig. 3.7 Trigger Delay Set-up Screen

To delay the stopping of recording ("storage") of data past the occurence of the trigger condition, a number of samples can be defined before the data recording really stops.

Use the keypad to enter (in the top field) the number of qualified clocks after the trigger condition occurrence at which recording (storage) should stop. This top-field value is the "trigger delay".

Or, to begin recording at a selected number of clocks after of before the trigger condition occurrence, enter that number of clocks in the second field, then select "A" (after) or "B" (before) in the third field. A sufficiently long trigger delay will place the entire recording interval after the trigger condition.

Only one of the two clock-number fields need to be entered; the corresponding number in the other number field will be automatically displayed. The distance between these two numbers is the record depth. The delay period includes only clock-qualified and data-qualified clocks.

#### NOTE :

The number of samples as trigger delay can be set on values lower than 17. Because the PM 3632's internal configuration, a minimum of 17 clocks must occur after the trigger condition for correct operation. These 17 clocks are automatically accounted for in all displays; the user need not be concerned about them unless the external clock stops within 17 clocks of the trigger event.

## 4.3 LIST DISPLAY

### 4.3.1 INTRODUCTION

The List Display is shown after pressing the LIST key.

Two main list displays are possible:

-The Logic (or Fast) Pod List display (fig. 4.2)

-The Micro-processor List display (fig. 4.3).

```

BIN OCT DEC HEX

TRIG 00000000 000 000

00

00001 00000000 000 000

00

00002 00000000 000 000

00

00003 00000000 000 000

00

00004 00000000 000 000

00

00005 00000000 000 000

00

00006 00000000 000 000

00

00007 00000000 000 000

ЙΝ

00008 00000000 000 000

00

00009 000000000 000 000

ЙΘ

00010 00000000 000 000

00

00011 00000000 000

000

00

00012 00000000 000 000

00

00013 00000000 000 000

00

fl=position cursor

f2=cursor spd: slow

Н

```

Fig. 4.2 Logic Pod List Display (LOGIC 32)

```

ADR DAT

STATE BIN

ST

0000 1001

9BE4

01

TRIG

00001 0000 1011 0094

C2

00002 0000 1010 0095

89

00003 0000 1010 0096

00

00004 0000 1011 0089

29

00005 0000 1011 008A

74

00006 0000 1001 3708

37

00007 0000 1011 008B

75

00008 0000 1001 3708

CS

00009 0000 1011 0080

D2

00010 0000 1010 008D

92

00011 0000 1010 008E

00

00012 0000 1011 008F

19

00013 0000 1011 0090

74

fl=position cursor A

f2=cursor spd: slow

```

Fig. 4.3 Microprocessor Pod List Display (8085)

Each line of this screen represents one data sample, displayed in bit groupings and number base as selected in the Display Format screen. The trigger condition (or the first data-qualified word in storage which follows the trigger condition), if present in memory, is labelled "TRIG".

To display the trigger condition, scroll up or down via the arrow keys, or move directly to the Triggerword by pressing the LIST key a second time.

To scroll up or down through the data samples, use the arrow keys.

### 4.3.2 MEMORY A or B?

When the PM 3632 has been provided with an optional Setup/Data-Memory (PM 8880/50), selection can be made to display the A or the B memory. The A or B is shown on the bottom line on the display. Selection is executed by pressing the A or the B key. Refer to the description of the PM 8880/50 (chapter 6).

#### 4.3.3 LOGIC POD LIST DISPLAY

Figure 4.2 shows an example of a Logic Pod data list display.

STATE column

This column indicates the sequence of the samples. When the Triggerword is <u>in</u> the acquisition memory, the numbers in this column are related to the Triggerword. When the Triggerword is <u>not in</u> the acquisition memory, these numbers represent the acquisition memory addresses.

DATA Columns (BIN, OCT, DEC, HEX or ASC)

These columns show the input signals. The display format, as well as the number-base is as selected in the FORMAT display. Each column is displayed with the l.s. digit at the right-hand side.

### 4.3.4 MICROPROCESSOR POD LIST DISPLAY

Figure 4.3 shows an example of a Microprocessor Pod data list display.

BIN column

This column represents the signals as connected to the side-inputs of the Microprocessor Pod. The number-base of this column can be changed in the FORMAT display.

Refer to the description of the specific Pod (chapter 5).

### 4.3 LIST DISPLAY

#### 4.3.1 INTRODUCTION

The List Display is shown after pressing the LIST key.

Two main list displays are possible:

-The Logic (or Fast) Pod List display (fig. 4.2)

-The Micro-processor List display (fig. 4.3).

```

STATE

BIN OCT DEC HEX

TRIG 00000000 000 000

ЯΘ

00001 00000000 000 000

00

00002 00000000 000 000

00

00003 00000000 000 000

00

00004 00000000 000 000

00

00005 00000000 000 000

00

00006 00000000 000 000

00

00007 00000000 000 000

00

00008 00000000 000 000

00

00009 00000000 000 000

00

00010 00000000 000

000

00

00011 00000000 000

000

00

00012 00000000 000 000

00

00013 00000000 000 000

00

f1=position cursor

Ĥ

f2=cursor spd: slow

```

Fig. 4.2 Logic Pod List Display (LOGIC 32)

```

ADR DAT

STATE BIN

ST

TRIG 0000 1001

00001 0000 1011

9BE4

01

0094

00002 0000 1010 0095

89

00003 0000 1010 0096

00

00004 0000 1011 0089

29

00005 0000 1011 008A

74

00006 0000 1001 3708

37

00007 0000 1011 008B

75

00008 0000 1001 3708

C8

00009 0000 1011 0080

D2

00010 0000 1010 008D

92

00011 0000 1010 008E

00

00012 0000 1011 008F

19

00013 0000 1011 0090

74

fl=position cursor A

f2=cursor spd: slow

```

Fig. 4.3 Microprocessor Pod List Display (8085)

Each line of this screen represents one data sample, displayed in bit groupings and number base as selected in the Display Format screen. The trigger condition (or the first data-qualified word in storage which follows the trigger condition), if present in memory, is labelled "TRIG".

To display the trigger condition, scroll up or down via the arrow keys, or move directly to the Triggerword by pressing the LIST key a second time.

To scroll up or down through the data samples, use the arrow keys.

#### 4.3.2 MEMORY A or B?

When the PM 3632 has been provided with an optional Setup/Data-Memory (PM 8880/50), selection can be made to display the A or the 8 memory. The A or B is shown on the bottom line on the display. Selection is executed by pressing the A or the B key. Refer to the description of the PM 8880/50 (chapter 6).

## 4.3.3 LOGIC POD LIST DISPLAY

Figure 4.2 shows an example of a Logic Pod data list display.

STATE column

This column indicates the sequence of the samples. When the Triggerword is <u>in</u> the acquisition memory, the numbers in this column are related to the Triggerword. When the Triggerword is <u>not in</u> the acquisition memory, these numbers represent the acquisition memory addresses.

DATA Columns (BIN, OCT, DEC, HEX or ASC)

These columns show the input signals. The display format, as well as the number-base is as selected in the FORMAT display. Each column is displayed with the l.s. digit at the right-hand side.

### 4.3.4 MICROPROCESSOR POD LIST DISPLAY

Figure 4.3 shows an example of a Microprocessor Pod data list display.

BIN column

This column represents the signals as connected to the side-inputs of the Microprocessor Pod. The number-base of this column can be changed in the FORMAT display.

Refer to the description of the specific Pod (chapter 5).

## ST column

This column shows the microprocessor-status, such as instruction-fetch, memory-write, wait-state etc. For the explanation of the status refer to the description of the specific Pod (chapter 5).

### ADR column

This column shows the address related to the microprocessor action.

## OAT column

This column shows the data related to the microprocessor action.

#### 4.4 DISASSEMBLY DISPLAY

### 4.4.1 INTRODUCTION

The Disassembly Display is shown after pressing the DISA key.

```

DISASSEMBLY

BUS ACTIVITY

STATE

PC

00001 0094 JP

NZ,0089

00004 0089 ADD

HL, HL

00005 008A LD

(HL), H

3708<37

(HL), L

00007 008B LD

37C8<C8

00009 008C JP

NC,0092

00012 008F ADD

HL, DE

00013 0090 LD

(HL), H

3872<38

(HL),L

00015 0091 LD

3872<72

00017 0092 DEC

A

00018 0093 LD

(HL), A

3872<00

00020 0094 JP

NZ,0089

00023 0097 JP

0000

00026 0000 RESET

00026 0000 DI

Cursor (f2): slow

Position Cursor: fl

```

Fig. 4.4 Disassembly Display Screen

The Disassembly mode displays data collected via an (optional) micro-processor pod, which enables the PM 3632 to display the recorded data as assembly-language micro-processor instructions ("reverse assembly").

When data qualification is being used, some ambiguities in the recorded data may result.

## 4.4.2 STATE column

This column shows the State numbers corresponding with the normal LIST display.

Note that not all State numbers are displayed, because each complete microprocessor instruction is displayed on one line.

The TRIG condition is only shown if the word which completes the trigger condition contains the first byte of the instruction.

# 4.4.3 PC column

This column shows the contents of the microprocessor-programmcounter at the instruction fetch (first byte).

#### 4.4.4 DISASSEMBLY column

This column shows the Mnemonics of the disassembled microprocessor-instructions.

For explanation of the Mnemonics refer to the microprocessor-handbooks.

## 4.4.5 BUS ACTIVITY column

This column shows the actual data transfers on the microprocessor bus.

E.g. 0800->16 The contents of memory-address 0800(H)=16 0801<-00 00 is written into memory address 0801(H)

|  |  | 20. |      |

|--|--|-----|------|

|  |  |     |      |

|  |  |     |      |

|  |  |     |      |

|  |  |     |      |

|  |  |     |      |

|  |  |     |      |

|  |  |     |      |

|  |  |     |      |

|  |  |     |      |

|  |  | +0  |      |

|  |  | 71  |      |

|  |  |     |      |

|  |  |     |      |

|  |  |     |      |

|  |  |     |      |

|  |  |     |      |

|  |  |     |      |

|  |  |     |      |

|  |  |     |      |

|  |  |     |      |

|  |  |     |      |

|  |  |     |      |

|  |  |     |      |